### MINISTRY OF EDUCATION AND SCIENCE OF UKRAINE

# KHARKOV NATIONAL UNIVERSITY OF RADIOELECTRONICS

ISBN 966-659-113-8

# Proceedings of IEEE East-West Design & Test Workshop (EWDTW'06)

Copyright © 2006 by The Institute of Electrical and Electronics Engineers, Inc.

Sochi, Russia, September 15 – 19, 2006

# **CONTENTS**

| A Black-Box-Oriented Test Methodology  A. Benso, A. Bosio, P. Prinetto, A. Savino                                                                                | . 11 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| Design and Optimization of Fault-Tolerant Distributed Real-Time Systems  Peng Z., Izosimov V., Eles P., Pop P                                                    | . 16 |

| Interconnect Yield Improvement for Networks on Chip  Andre Ivanov                                                                                                | . 22 |

| The Scaling Semiconductor World and Test Technology  Yervant Zorian                                                                                              | . 22 |

| A Unified HW/SW Interface Model to Remove Discontinuities Between HW and SW Design  A. Jerraya                                                                   | . 23 |

| Background Cache for Improving Memory Fault Tolerance  Michail F. Karavay, Vladimir V. Sinelnikov                                                                | . 24 |

| Factors in High-Speed Wireless Data Networking – New Ideas and a New Perspective  Daniel Foty                                                                    | . 29 |

| Hierarchical Silicon Aware Test and Repair IP: Development and Integration Flow Reducing Time to Market for Systems on Chip Samvel Shoukourian, Yervant Zorian   | . 39 |

| The Pivotal Role of Performance Management in IC Design  Eyck Jentzsch                                                                                           | . 41 |

| TEST METHODS AND TOOLS                                                                                                                                           |      |

| Analysis of a Test Method for Delay Faults in NoC Interconnects  Tomas Bengtsson, Artur Jutman, Shashi Kumar, Raimund Ubar, Zebo Peng                            | . 42 |

| Unified Framework for Logic Diagnosis A. Rousset, P. Girard, S. Pravossoudovitch, C. Landrault, A. Virazel                                                       | . 47 |

| Hierarchical Systems Testing based on Boundary Scan Technologies  Hahanov V., Yeliseev V., Hahanova A., Melnik D                                                 | . 53 |

| Testing the Hardware Implementation of a Distributed Clock Generation Algorithm for SoCs  A. Steininger, T. Handl, G. Fuchs, F. Zangerl                          | . 59 |

| Extended Boundary Scan Test Using Hybrid Test Vectors  Jan Heiber                                                                                                | . 65 |

| A March Test for Full Diagnosis of All Simple Static Faults in Random Access Memories  G. Harutunyan, Valery A. Vardanian                                        | . 68 |

| Efficient Implementation of Physical Addressing for Testing and Diagnosis of Embedded SRAMs for Fa<br>Coverage Improvement<br>K. Aleksanyan, Valery A. Vardanian |      |

| High Level Models Based Functional Testing of Pipelined Processors                                                                                               | 76   |

| On Complexity of Checking of Cryptosystems  Volodymyr G. Skobelev                                                                                                                                                            | 82 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Distributed Fault Simulation and Genetic Test Generation of Digital Circuits  Skobtsov Y.A., El-Khatib A.I., Ivanov D.E                                                                                                      | 89 |

| Hierarchical Evolutionary Approach to Test Generation Skobtsov V.Y. Skobtsov Y.A                                                                                                                                             | 95 |

| VERIFICATION                                                                                                                                                                                                                 |    |

| Incremental ABV for TLtoRTL Design Refinement Nicola Bombieri, Franco Fummi, Graziano Pravadelli1                                                                                                                            | 00 |

| RTL Compiler Templates Verification: Approach to Automation  Lev Danielyan, Sergey Hakobyan1                                                                                                                                 | 08 |

| Verification of Implementation of Parallel Automata (Symbolic Approach)  Andrei Karatkevich1                                                                                                                                 | 12 |

| SystemCFL: An Infrastructure for a TLM Formal Verification Proposal (with an overview on a tool set for practical formal verification of SystemC descriptions)  K.L. Man, Andrea Fedeli, Michele Mercaldi, M.P. Schellekens1 |    |

| System Level Methodology for Functional Verification SoC Alexander Adamov, Sergey Zaychenko, Yaroslav Miroshnychenko, Olga Lukashenko1                                                                                       | 22 |

| Path Sensitization at Functional Verification of HDL-Models  Alexandr Shkil, Yevgeniya Syrevitch, Andrey Karasyov, Denis Cheglikov1                                                                                          | 26 |

| Dynamic Register Transfer Level Queues Model for High-Performance Evaluation of the Linear Tempor Constraints  Vladimir Hahanov, Oleg Zaharchenko, Sergiy Zaychenko1                                                         |    |

| The Automation of Formal Verification of RTL Compilers Output  Pavlush Margarian                                                                                                                                             |    |

| LOGIC, SYSTEM AND PHYSICAL SYNTHESIS                                                                                                                                                                                         |    |

| Congestion-Driven Analytical Placement Andrey Ayupov, Alexander Marchenko1                                                                                                                                                   | 43 |

| Estimation of Finite State Machine Realization Based on PLD  E. Lange, V. Chapenko, K. Boule1                                                                                                                                | 49 |

| Encoding of Collections of Fragment of Variables  Barkalov A.A., Ahmad Fuad Bader, Babakov R.M1                                                                                                                              | 53 |

| An Algorithm of Circuit Clustering for Logic Synthesis  O. Venger, I. Afanasiev, Alexander Marchenko1                                                                                                                        | 56 |

| CMOS Standard Cell Area Optimization by Transistors Resizing  Vladimir Rozenfeld, louri Smirnov, Alexander Zhuravlev1                                                                                                        | 63 |

| Optimization of Address Circuit of Compositional Microprogram Unit Wisniewski R., Alexander A. Barkalov, Larysa A. Titarenko1                                                                                                | 67 |

| Optimization of Circuit of Control Unit with Code Sharing  Alexander Barkalov, Larysa Titarenko, Małgorzata Kołopieńczyk                                                                                | 171 |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Routing a Multi-Terminal Nets with Multiple Hard Pins by Obstacle-Avoiding Group Steiner Tree Construction  J. D. Cho, A. I. Erzin, V. V. Zalyubovsky                                                   | 175 |

| Optimization for Electro- and Acousto-Optical Interactions in Low-Symmetric Anisotropic Materials Kajdan Mykola, Laba Hanna, Ostrovskij Igor, Demyanyshyn Nataliya, Andrushchak Anatolij, Mytsyk Bohdan | 179 |

| Force-Position Control of the Electric Drive of the Manipulator  A.V. Zuev, V.F. Filaretov                                                                                                              | 184 |

| FAULT TOLERANCE                                                                                                                                                                                         |     |

| K-out-of-n and K(m,n) Systems and their Models Romankevych V., Potapova K., Hedayatollah Bakhtari                                                                                                       | 189 |

| Fault Tolerant Systems with FPGA-based Reconfiguration Devices  Vyacheslav S. Kharchenko, Julia M. Prokhorova                                                                                           | 190 |

| Fault-Tolerant Infrastructure IP-cores for SoC: Basic Variants and Realizations Ostroumov Sergii, Ushakov A. A., Vyacheslav S. Kharchenko                                                               | 194 |

| Fault-tolerant PLD-based Systems on Partially Correct Automatons  Nataliya Yakymets, Vyacheslav Kharchenko                                                                                              | 198 |

| FME(C)A-Technique of Computer Network Reliability and Criticality Analysis  Elyasi Komari Iraj, Anatoliy Gorbenko                                                                                       | 202 |

| TEST GENERATION AND TESTABILITY                                                                                                                                                                         |     |

| Scan Based Circuits with Low Power Consumption Ondřej Novák, Zdeněk Plíva                                                                                                                               | 206 |

| Memory Address Generation for Multiple Run March Tests with Different Average Hemming Distance S.V. Yarmolik, V.N. Yarmolik                                                                             |     |

| Structural Method of Pseudorandom Fixed Weight Binary Pattern Sequences Generation  Romankevych A., Grol V., Fallahi Ali                                                                                | 217 |

| Test Pattern Generation for Bridge Faults Based on Continuous Approach  N. Kascheev, F. Podyablonsky                                                                                                    | 222 |

| Hierarchical Analysis of Testability for SoCs  Maryna Kaminska, Vladimir Hahanov, Elvira Kulak, Olesya Guz                                                                                              | 226 |

| Embedded Remote Wired or Wireless Communication to Boundary-Scan Architectures  Mick Austin, Ilkka Reis, Anthony Sparks                                                                                 | 231 |

| Economics Modeling the DFT of Mixed-Signal Circuits Sergey G. Mosin                                                                                                                                     | 236 |

| CAD TOOLS AND DEVICES                                                                                                                                                                                   |     |

| Optimal Electronic Circuits and Microsystems Designer  A.I. Petrenko                                                                                                                                    | 239 |

| Computer Aided Design Support of FSM Multiplicative Decomposition  Alexander Sudnitson, Sergei Devadze                                                               | 241 |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Complex Process Engineering of Projection of Electronic Devices by Means of Automized System SATURN  D.V. Bagayev, A.C. Firuman                                      | 247 |

| Hand-Held Mobile Data Collecting Terminal  Armen Saatchyan, Oleg Chuvilo, Chaitanya Mehandru                                                                         | 252 |

| Logic and Fault Simulation Based on Multi-Core Processors Volodymyr Obrizan, Valeriy Shipunov, Andiry Gavryushenko, Oleg Kashpur                                     | 255 |

| HES-MV – A Method for Hardware Embedded Simulation  Vladimir Hahanov, Anastasia Krasovskaya, Maryna Boichuk, Oleksandr Gorobets                                      | 257 |

| Hierarchical Approach for Functional Verification of HW/SW System on Chip (SoC)  Oleksandr Yegorov, Podkolzin N., Yegor Denisov, Andrey Yazik                        | 264 |

| Output Buffer Reconfiguration in Case of Non Uniform Traffic  Vyacheslav Evgrafov                                                                                    | 267 |

| DESIGN METHODS AND MODELING                                                                                                                                          |     |

| Time-Sensitive Control-Flow Checking Monitoring for Multitask SoCs Fabian Vargas, Leonardo Picolli, Antonio A. de Alecrim Jr., Marlon Moraes, Márcio Gama            | 272 |

| Development and Application of FSM-Models in Active-HDL Environment for Network Protocols Tes Anna.V. Babich, Oleksandr Parfentiy, Eugene Kamenuka, Karina Mostovaya |     |

| How to Emulate Network-on-Chip?  Peeter Ellervee, Gert Jervan                                                                                                        | 282 |

| Multistage Regular Structure of Binary Counter of ones Arbitrary Modulo Saposhnikov V. V., Saposhnikov VL. V., Urganskov D. I.                                       | 287 |

| An Enhanced Analogue Current-Mode Structure of WP Control Circuit of Neural Networks  Hossein Aghababa, Leyla S.Ghazanfari, Behjat Forouzandeh                       | 291 |

| One-Parameter Dynamic Programming Algorithm for Optimal Wire Selection Under Elmore Delay MA.I. Erzin, V.V. Zalyubovsky                                              |     |

| Analytical Model of Clock Skew in Buffered H-Trees  Dominik Kasprowicz                                                                                               | 301 |

| High-Level Facilities for Modeling Wireless Sensor Networks  Anatoliy Doroshenko, Ruslan Shevchenko, Konstantin Zhereb                                               | 305 |

| Class E Power Amplifier for Bluetooth Applications Olga Antonova, George Angelov, Valentin Draganov                                                                  | 311 |

| An Automation Method for Gate-Count Characterization of RTL Compilers  Arik Ter-Galstyan                                                                             | 313 |

| Algorithmic Method of The Tests Forming for Models Verification of Microcircuits Memory  M.K. Almaid, V.A. Andrienko, V.G. Ryabtsev                                  | 317 |

| SUM IP Core Generator – Means for Verification of Models–Formulas for Series Summation in RKHS Vladimir Hahanov, Svetlana Chumachenko, Olga Skvortsova, Olga Melnikova |       |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| Design of Wavelet Filter Bank for JPEG 2000 Standard<br>Hahanova I.V., Hahanov V.I., Fomina E., Bykova V., Sorudeykin K                                                | . 327 |

| Design of Effective Digital Filters in FPGA Pavel V. Plotnikov                                                                                                         | . 332 |

| POSTER SESSION                                                                                                                                                         |       |

| Applications of Combinatorial Cyclic Codes for Images Scan and Recognition  Vladimir Valkovskii, Dmitry Zerbino, Oleg Riznyk                                           | . 335 |

| Architecture of Internet Access to Distributed Logic Simulation System  Ladyzhensky Y.V., Popoff Y.V.                                                                  | . 339 |

| Computer System Efficient Diagnostics with the Usage of Real-Time Expert Systems  Gennady Krivoulya, Alexey Lipchansky, Olga Korobko                                   | . 344 |

| DASPUD: a Configurable Measurement Device<br>Nikolay P. Molkov, Maxim A. Sokolov, Alexey L. Umnov, Dmitry V. Ragozin                                                   | . 348 |

| Design Methods of Self-Testing Checker for Arbitrary Number of Code Words of (m,n) Code Yu. B. Burkatovskaya, N.B. Butorina, A. Yu. Matrosova                          | . 355 |

| Dynamic Heat and Mass Transfer in Saline Water due to Natural Convection Flow over a Vertical Flat<br>Plate<br>Rebhi A. Damseh                                         |       |

| Effect of Driving Forces On Cylindrical Viscoelastic Fluid Flow Problems  A. F. Khadrawi, Salwa Mrayyan, Sameh Abu-Dalo                                                |       |

| Evolutional Methods for Reduction of Diagnostic Information  D. Speranskiy                                                                                             |       |

| Evolutionary Algorithms Design: State of the Art and Future Perspectives  Yuri R. Tsoy                                                                                 |       |

| Functional properties of faults on fault-secure FSM design with observing only FSM outputs  S. Ostanin                                                                 | . 380 |

| Hardware Methods to Increase Efficiency of Algorithms for Distributed Logic Simulation  Ladyzhensky Y.V., Teslenko G.A                                                 | . 385 |

| Information Embedding and Watermarking for Multimedia and Communication  Aleksandr V. Shishkin                                                                         | . 386 |

| Low Contrast Images Edge Detector<br>I.V. Ruban, K.S. Smelyakov, A.S. Smelyakova, A.I. Tymochko                                                                        | . 390 |

| Minimization of Communication Wires in FSM Composition S.V. Zharikova, N.V. Yevtushenko                                                                                | . 397 |

| Neuro-Fuzzy Unit for Real-Time Signal Processing                                                                                                                       | . 403 |

| On Decomposition of Petri Net by Means of Coloring  Wegrzyn Agnieszka407                                                                                                               |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Single-Argument Family of Continuous Effectively Computed Wavelet Transforms  Oleg E. Plyatsek, Majed Omar Al-Dwairi414                                                                |

| Synthesis Methods of Finite State Machines Implemented in Package ZUBR<br>Valery Salauyou, Adam Klimowicz, Tomasz Grzes, Teodora Dimitrova-Grekow, Irena Bulatowa. 420                 |

| Synthesis of Logic Circuits on Basis of Bit Transformations Yuri Plushch, Alexander Chemeris, Svetlana Reznikova423                                                                    |

| System of K-Value Simulation for Research Switching Processes in Digital Devices  Dmitrienko V.D., Gladkikh T.V., Leonov S.Yu428                                                       |

| Test Points Placement Method for Digital Devices Based on Genetic Algorithm  Klimov A.V., Speranskiy D.V436                                                                            |

| The Approach to Automation of Designing Knowledge Base in the Device-Making Industry  O.V. Bisikalo440                                                                                 |

| The Optimal Nonlinear Filtering of Discrete-Continuous Markovian Processes in Conditions of Aposteriory Uncertainty  Victor V. Panteleev                                               |

| The Realization of Modified Artificial Neural Network for Information Processing with the Selection of Essential Connections by the Program Meganeuro  E.A. Engel                      |

| Web-system Interface Prototype Designing Globa L.S., Chekmez A. V., Kot T. N453                                                                                                        |

| A Bio-Inspired Method for Embedded System Scheduling Problems  Abbas Haddadi, Saeed Safari, Behjat Forouzandeh456                                                                      |

| Iterative Array Multiplier with On-Line Repair of Its Functions  Drozd A., Lobachev M., Reza Kolahi, Drozd J461                                                                        |

| Mathematical Modeling and Investigation of a Main SDH-Network Structural Reliability  M.M. Klymash, I.M. Dronyuk, R.A. Burachok464                                                     |

| Experimental Investigation of Two Phase Flow Pressure Drop and Contraction on Tee Junction Shannak Benbella, Al-Qudah Kalid, Al-Salaymeh Ahmed, Hammad Mahmoud, Alhusein Mahmoud . 467 |

| Application of Adaptive and New Planning Methods to Solve Computer-Aided Manufacturing Problems Nevludov I.Sh., Litvinova E.I., Evseev V.V., Ponomarjova A.V472                        |

| Petri Net Decomposition Algorithm based on Finding Deadlocks and Traps  Agnieszka Wegrzyn, Marek Wegrzyn477                                                                            |

| Testing for Realistic Spot Defects in CMOS Technology: a Unified View  Michel Renovell                                                                                                 |

| AUTHORS INDEX 483                                                                                                                                                                      |

# Hierarchical Systems Testing based on Boundary Scan Technologies

Vladimir Hahanov, Vladimir Yeliseev, Anna Hahanova, Dmytro Melnik

Design Automation Department

Kharkiv National University of Radio Electronics, 14 Lenin Ave., 61166, Ukraine

hahanov@kture.kharkov.ua

### Abstract

We propose models of complex program-technical systems testing; these models solve diagnosis tasks in real time. Models use IEEE standard boundary scan technologies to observe internal lines, and methods of testability evaluation to define critical places in digital objects. Models and methods are oriented to test distributed control systems of critical technologies.

### 1. Introduction

Basic requirements for modern informational and control systems for complex objects and critical technologies [1-5] are: 1) provide high reliability during operation [5]; 2) online monitoring and control of all the parameters of critical system of object; 3) testing, diagnostics and repair in technically and standard acceptable time; 4) provide desired diagnosis depth of system or its components, automatically and in real time.

New generation of modern technologies and design flows introduces additional criteria, related to design, manufacture and operation of digital devices: time-to-market, Design-for-Manufacturability, Testability, Diagnosis, Verification [6-8]. Major design stage is verification process, aimed to eliminate all design errors on the early stages; it leads to considerable time and costs savings. Acceptable testable overhead (assertion), added at early design stage, is interesting here, because it considerable decreases main parameter – time-to-market, using verification and testing methods; it is very urgent and attractive design model [2-4, 10].

Talk is about use of verification test, obtained at system design stage, to check device with minimal additional hardware and software expenses using boundary scan technologies [6, 9]. At the same time, hardware/software overhead mechanism must include

additional control points, which must be introduced into design using Boundary Scan Register of special (ad-hoc) technologies at synthesis stage. As a result, design redundancy created once maybe used many times to check components of digital system during all stages of its lifecycle.

At present, complex digital devices are considered as objects with several levels of hierarchy. At the lowest level, system is represented as a set of modern integrated circuits (PLD, ASIC), which implements SoCs, NoCs, memory, processors. Second level is formed by system on boards, where integral circuits are represented as primitives. Third level represents set of boards, which integrated into crates. Fourth level combines set of crates or boxes into complex distributed control system of technological process, manufacturing or critical technologies (aviation, nuclear-power engineering, cosmonautics, meteorology, defense, ecology) [5]. Fifth level may be considered as geographically distributed system, e.g. Internet. In this research, we consider from first to fourth levels of hierarchy, in order to creation of models and methods of its testing with defined diagnosis depth.

Research objective — considerable decrease of complex digital system testing time during operation based on creation of general model of organization and execution of diagnostic experiment, including unconditional algorithms of faults finding using IEEE standards of testable design [6-9].

Research problems: 1) choosing appropriate methods and tools for testing of all mentioned levels of hierarchy; 2) development of hierarchical model of organization and execution of diagnostic experiment, including conditional and unconditional algorithms of faults finding, oriented to testable design standards; 3) practical implementation of complex digital devices testing models and experimental evaluation.

# 2. Digital system testing model

Object of inquiry – digital control system, represented as several levels of hierarchy, designed using IEEE testable design standards. Especially, we consider program-technical complex F, as unit-undertest, which can be represented as tuple:  $F = \langle C,B,P,M \rangle, \text{ where } C = \{c_1,c_2,...,c_n\} - \text{finite nonempty set of crates in digital system, } B = \{b_1,b_2,...,b_m\} - \text{ set of boards in crate, } P = \{p_1,p_2,...,p_k\} - \text{ set of integral circuits on board, } M = \{m_1,m_2,...,m_g\} - \text{ set of functional IP-Cores on chip (integrated circuit). At the same time, following conditions of folding or hierarchy are true:}$

$$m_{ijrs} \in p_{ijr} \in b_{ij} \in c_i \in F, (i = \overline{1,n}; j = \overline{1,m}; r = \overline{1,k}; s = \overline{1,g}) (1)$$

General equation of diagnosis for considered object of research maybe represented as following:

$$\begin{split} D = R^* \wedge L = (R^+ \oplus R^-) \wedge L = [(T \oplus F) \oplus (T \oplus F^*)] \wedge L \, (2) \\ \text{where formula's parameters are defined as: } D - \text{set of} \\ \text{detected faults during testing; } L(T_i) - \text{fault list,} \\ \text{detectable by test pattern } T_i \in T = (T_1, T_2, ..., T_i, ..., T_h) \, , \\ \text{represented in the form of table} \end{split}$$

$$L(t_i) = [L_{ij}], i = \overline{1,p}; j = \overline{1,q},$$

where each test is associated with subset of detectable faults, p – number of observed outputs, q – whole number of lines;  $R^-(T_1) = (R_1^-, R_2^-, ..., R_1^-, ..., R_p^-)$  – binary vector of experimental check (VEC), equal to number of observed outputs;  $R^+(T_1) = (R_1^+, R_2^+, ..., R_1^+, ..., R_p^+)$  – reference vector of outputs' states; F – reference device model;  $F^*$  – real device.

For diagnosis process organization, vector  $R^*(T_i) = (R_1^*, R_2^*, ..., R_i^*, ..., R_p^*)$  is formed correspondingly to the following rule:

$$R_i^* = R_i^+ \oplus R_i^-. \tag{3}$$

Ideal model for fault diagnosis is represented as the following structure:  $F = \{T \times L \times R\}$ . But complexity of such 3D table is defined as:  $|F| = h \times 2q \times p$ .

If test's dimension, in the best case, is square of number of lines, then this equation transforms to the following:  $|F| = \{q^2 \times 2q \times p\} = 2q^3p \approx q^4$ . If number of lines is from 100 000 to 1 000 000, then power of diagnosis table will be in interval  $10^{20} \ge |F| \ge 10^{24}$ . Naturally, such amount of diagnostic information is impossible to process to find fault in digital system.

Data compression problem has occurred. In fact, we can compress all of three components {T, L, R} [11]: test, fault lists, output responses, but at the same time we loose diagnosis accuracy or diagnostic experiment time. Further, we propose diagnosis method with maximum possible diagnosis depth, based on real-time diagnostic experiment, when we can exclude parameter T, and whole data can be represented as 2D table, because we lost test length information. We propose the following diagnostic model:

$$\begin{cases} L(T_i) = F \oplus T_i; \\ R^*(T_i) = f(F, T_i, D^*); \\ D(T_i) = g[L(T_i), R^*(T_i)]. \end{cases}$$

$$\begin{cases} D^S(T_i) = \bigwedge_{\forall j (R_j^* = 1)} L_j \& \overline{\bigvee_{\forall j (R_j^* = 0)}} L_j; \\ \nabla^m(T_i) = \bigvee_{\forall j (R_j^* = 1)} L_j \& \overline{\bigvee_{\forall j (R_j^* = 0)}} L_j. \end{cases}$$

$$\begin{cases} D_0^S(T) = D_0^S(T) \vee D^S(T_i) \& S^+(T_i); \\ D_1^S(T) = D_1^S(T) \vee D^S(T_i) \& \overline{S}^+(T_i). \end{cases}$$

$$\begin{cases} D_0^m(T) = D_0^m(T) \vee D^m(T_i) \& \overline{S}^+(T_i). \end{cases}$$

$$\begin{cases} D_0^m(T) = D_0^m(T) \vee D^m(T_i) \& \overline{S}^+(T_i). \end{cases}$$

$$\begin{cases} D_1^m(T) = D_1^m(T) \vee D^m(T_i) \& \overline{S}^+(T_i). \end{cases}$$

First three equations present procedures: forming detectable fault lists; calculating output responses; detecting actual faults during real experiment. Second equations system allows defining single or multiple stuck-at faults by executing two operations on the fault table L, detectable by input sequence  $T_i$  and vector of experimental check  $R^*$ . Third equations system allows calculating vector of single faults, detected during test process, as function of fault-free vector  $S^+(T_i)$  and complete test T. Fourth equations system allows collecting multiple faults into vector, detected during test process, also as function of fault-free vector  $S^+(T_i)$ . The real-time diagnostic experiment result is set of single or multiple faults, detected in digital system. At the same time, memory consumption is:

$$Q^{M} = (p^{X} \times q^{2}) + (q \times p) + 7q + 3p.$$

(5)

If we use built-in test pattern generator, so it is no need to store test data, then amount of memory will be minimal:

$$Q_{A}^{M} = (q \times p) + 7q + 3p.$$

(6)

Naturally, computational complexity is function of memory consumption, provided with (5) and (6).

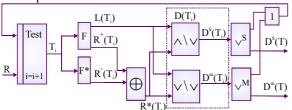

Fig. 1 represents structure of processor to perform diagnostic experiment, which built on equations (4).

Advantage of this processor is ease of performing table and vector operations, which can be implemented both in computer and PLD.

Figure 1. Structure model of digital system diagnostics

As data structures example, necessary to perform the diagnostic experiment, we show tables and vectors to illustrate procedures, defined by mentioned processor (fig. 1) and equations (4):

Here we consider unit under diagnostics, having 4 outputs (p=4) with associated fault list, equal to number of lines (q=8). Detectable fault is identified with 1, undetectable one - with 0. Type of stuck-at fault is defined by inverted fault-free value of corresponding line in S<sup>+</sup>(T<sub>i</sub>). Values of vector of experimental check are calculated as XOR function of two vectors: fault free  $R^+(T_i)$  and actual results  $R^-(T_i)$ of real unit-under-test. Thus, one (zero) value of vector R\*(Ti) identifies coincidence (non-coincidence) of pattern and real responses. At the same time, we use two strategies: searching for single and multiple faults test-vector, shown each by vectors  $D^{S}(T_{i}), D^{m}(T_{i})$ correspondingly. Saving information is performed separately in vectors  $\label{eq:decomposition} D_0^s(\mathsf{T}), D_1^s(\mathsf{T}), D_0^m(\mathsf{T}), D_1^m(\mathsf{T})\,, \ \ \text{which} \ \ \text{form} \ \ \text{single}$ and multiple fault lists. Equations (3) and (4) are used.

Thus, for hierarchically complex digital system, it is more economically to execute diagnostic experiment in real-time. In this case, it is necessary to store information about output responses and fault simulation results.

### 3. Testing using IEEE standards

Main disadvantage of existing design methods and flows [20-22] is inability to insert self-testing hardware overhead. At the same time, overhead requires additional timing and money costs. Nevertheless, developers are trying to follow modern requirements and to comply to IEEE testable design standards. What do mentioned standards give in the view of test process and diagnostic result for complex hierarchical systems? Naturally, effectiveness criterion is considered: diagnostics time with desired quality, defined by fault location depth.

Existing methods have time-consuming and high-cost elementary checks, which help to identify type and location of fault in system. The best solution is to use unconditional experiment, which removes uncertainty of testing and diagnosis defining by including additional observation points based on existing IEEE standards.

Which lines do need additional observation? Such lines, that allow splitting equivalent faults [23] and make them diagnosable. E.g., if number of observable outputs is p, and test length is h, then q is number of detected faults and it is defined by the following equation:

$$q = 2^{p \times h} \quad (p \neq 0, h \ge 2) \tag{7}$$

But equivalent faults may be your best friend in huge designs with millions of gates. They may decrease size of test (parameter h), but also they make diagnostic properties very bad. To recover mentioned property, it is necessary to increase parameter p in equation (7). Thus, additional observable internal lines increase diagnostic depth.

CAMELOT ideology [8, 13] is used to find additional observable lines. They are defined by calculation of observability  $O(X_i)$  for each internal variable. Then we need to select a set of such lines  $X_i$  provided that predefined value of observability is reached:

$$X_i \in Y \leftarrow [O(X_i) \le \{O_{max}, T_{max}^*\} \lor X_i \in R].$$

(8)

It is necessary to exclude all input lines from set Y. Moreover, it is necessary to calculate controllability, observability and testability for each line. Thus, testability evaluation methods give ability to find bottlenecks in design in the view of controllability, observability and testability. Further, IEEE Boundary Scan Standards 1149.1 and IEEE P1500 [6,9] make

lines observable (controllable), due to scan technologies.

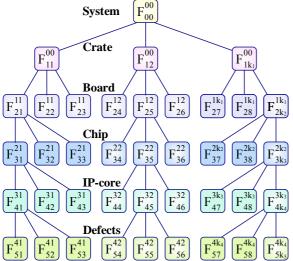

As to hierarchy of design, its structure may be represented as tree, where each node – component in relation to the higher level of hierarchy – having one input arc and several outgoing (see fig. 2).

Figure 2. Hierarchical model of complex digital system

Mathematical model of such hierarchy is represented as equations system:

$$\begin{cases} F = \begin{bmatrix} F_{ij}^{rs} \end{bmatrix}, & (i = \overline{0,5}; j = \overline{1,k}_{j}; r = \overline{0,4}; s = \overline{1,k}_{j-1}); \\ T = \begin{bmatrix} T_{ij}^{rs} \end{bmatrix}; & L = \begin{bmatrix} L_{ij}^{rs} \end{bmatrix}; \\ F_{ij}^{rs} \oplus T_{ij}^{rs} = L_{ij}^{rs}. \end{cases}$$

(9)

$\begin{array}{c} Complete \quad identifier \quad of \quad system's \quad component \\ F = \begin{bmatrix} F_{ij}^{IS} \end{bmatrix} \quad has \quad four \quad indexes. \quad Lower \quad indexes \quad (ij) \quad are \\ used \quad to \quad identify \quad level \quad of \quad hierarchy \quad and \quad number \quad of \quad identify \quad level \quad of \quad hierarchy \quad and \quad number \quad of \quad description. \\ \end{array}$

component. Upper indexes are used to identify relation to parent node.

There are two testing strategies. First one uses

functional test, which allows defining unit's fault. Only at the lowest level, test gives fault list. The second strategy is more intellectual due to complex and huge diagnostic tests. Testing of current component gives exact fault's address.

Test of higher level identifies faulty components of one lower level:

$$\begin{split} F_{1j}^{rs} \oplus T_{1j}^{rs} &= L_{1j}^{rs} = \{L_{21}^{1j}, L_{22}^{1j}, ..., L_{2k_{j}}^{1j}\}; \\ F_{2j}^{rs} \oplus T_{2j}^{rs} &= L_{2j}^{rs} = \{L_{31}^{2j}, L_{32}^{2j}, ..., L_{3k_{j}}^{2j}\}; \\ F_{3j}^{rs} \oplus T_{3j}^{rs} &= L_{3j}^{rs} = \{L_{41}^{3j}, L_{42}^{3j}, ..., L_{4k_{j}}^{3j}\}; \\ F_{4j}^{rs} \oplus T_{4j}^{rs} &= L_{4j}^{rs} = \{L_{51}^{4j}, L_{52}^{4j}, ..., L_{5k_{j}}^{4j}\}. \end{split}$$

$$(10)$$

One more test generation strategy: for each IP-core single stuck-at fault test is generated. Then, already generated tests are combined with upper level tests.

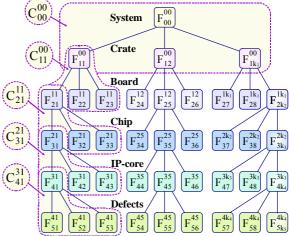

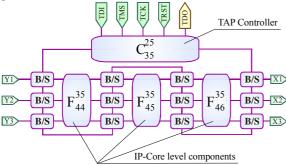

Following cooperation strategy of boundary scan technology with hierarchical object model illustrates accessibility to inputs and outputs of each component during diagnostic procedure (see fig. 3).

Figure 3. BS-wrapper of hierarchical model of digital system

Model of B/S-controller is universal in relation to parent node and nearest components-successors:

$$F_{ij}^{rs} = \{F_{i+1,1}^{ij}, F_{i+1,2}^{ij}, ..., F_{i+1,k_1}^{ij}\}. \tag{11}$$

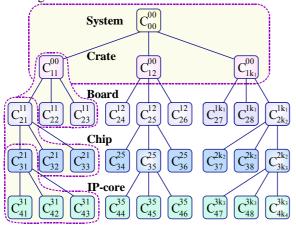

E.g., controller:  $C_{31}^{21} \approx F_{31}^{21} = \{F_{41}^{31}, F_{42}^{31}, F_{43}^{31}\}$ , see fig. 3, scans data in the one chip, containing three IP-cores:  $\{F_{41}^{31}, F_{42}^{31}, F_{43}^{31}\}$ . Applying equation (11) to system's model (see fig. 4), we may obtain hierarchical structure of B/S-controller, represented at fig. 4.

Hardware overhead of B/S testing system is 2-5% of whole functional component, which is acceptable for modern chip sets of companies like Xilinx and Altera. Performance overhead is no more than 0,5%. There is time consumption during diagnostic experiment. It can be calculated using equation:

$$Q(F) = \sum_{j=1,5} k_j \times p_j \times t^*.$$

(12)

$k_j$  – number of boundary scan registers at k-level of hierarchy,  $p_j$  – number of latches in register of j-level of hierarchy,  $t^*$  – information shift time. For 1 000 000 gates design, number of observable lines may be up to 1 000. In such case hardware overhead will be 2,1%, testing speed will be reduced in 1 000 times and will be not greater than 100 msec/test-vector.

Figure 4. Hierarchical structure of B/Scontrollers of complex system

Main idea of boundary scan standards is ease of control and observation of internal lines by using hardware overhead in form of Boundary Scan Register and Test Access Port controller. Typical B/S-structure is shown at fig. 5. Integrated circuit is divided into separate modules; tests and diagnostic algorithms are generated for them.

Figure 5. IEEE scan's standards circuit

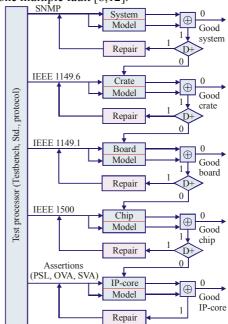

General test process model is shown at fig. 6. Principles of testing system organization:

- 1) Use the most appropriate IEEE standards [6-9] for verification of components on the current level of hierarchy;

- 2) Determine given depth diagnosis automatically, without using of conditional defect finding algorithms;

- 3) Only single component may be faulty;

- 4) Testing procedure after repair begins from the top level to low level of hierarchy descending diagnosis;

5) Testing procedure may begin from any level of hierarchy and may finish on the desired level by engineer.

Suggested testing model detects single fault and at least one multiple fault [8,12].

Figure 6. Testing structure for digital system

### 4. Conclusions

During current research international IEEE standards are considered, which are suitable for testing and diagnosis of program-technical complexes and broad range of electronic system: starting with components inside IC, ending with complex systems, consisting of boards and crates.

Considered IEEE standards 1149.1, 1149.4, 1149,6 and 1500 offer wide ability for solving tasks: component functional testing; interconnection testing; system on board functional testing; system on crate functional testing.

Units under test are: analog components; digital components; mixed components; discrete elements; printed circuit boards, consisting of mentioned components.

Scientific novelty of obtained results lies in using of ad hoc technologies, combining existing IEEE testability standards with specialized schematic solutions, which allow reducing in several times testing and diagnosis time of complex digital systems [11]:

- 1) Analytic and structure diagnostic models are presented aimed to real-time experiments using fault simulation;

- 2) Unit-hierarchical testing method is developed. Main idea is to represent system as hierarchy of simpler components. For this model, network of boundary scan registers is developed.

- 3) Suggested diagnostic method considerable decrease diagnostic information.

Thus, Boundary Scan technologies allow designers to meet the modern requirements and tendencies during design, verification, debug, manufacturing, testing, embedded software design and operation of different systems. Compliance of final software or hardware product to the international IEEE standards – is a guarantee of successful distribution on the world market.

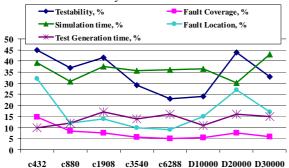

Practical importance lays in significant (50-70%) decrease of time for fault identification by using IEEE testability standards [5-7, 9]. At the same time, diagnostic depth is increased on 10-30% (fig. 7) with increased observability on 3%.

Figure 7. Digital system characteristics improvement

### 5. References

- [1] Grant Martin. The Reuse of Complex Architectures. IEEE Design and Test of Computers. November-December 2002. P. 4-6.

- [2] Rajesh K. Gupta and Yervant Zorian. Introducing Core-Based System Design. IEEE Design & Test of Computers. November-December 1997. P. 15-25.

- [3] Yervant Zorian. What is Infrustructure IP? IEEE Design & Test of Computers. May-June 2002. P. 5-7.

- [4] L. Benini and G. D. Micheli. Networks on chips: A new soc paradigm. IEEE Computer. Vol. 35. No. 1. 2002. P. 70–78

- [5] Yastrebenetskiy M.A., Vasilchenko V.M. i dr. Bezopasnost' atomnyh stanciy. Informacionnye i upravlyauyschie sistemy. Pod. red. M.A. Yastrebenetskogo. K.: Tehnika. 2004. 472 s. (In Russian)

- [6] IEEE P1500/D11. January 2005. Draft Standard Testability Method for Embedded Core-based Integrated Circuits. New York. 2005. 138 p.

- [7] Yervant Zorian. Test Requirements for Embedded Core-Based Systems and IEEE P1500. In Proceedings IEEE International Test Conference (ITC). Washington, DC. November 1997. IEEE Computer Society Press. P. 191-199.

- [8] Abramovici M., Breuer M.A. and Friedman A.D. Digital systems testing and testable design. Computer Science Press. 1998. 652 p.

- [9] IEEE Std 1149.6-2003. Standard for Boundary-Scan Testing of Advanced Digital Networks. New York. 2003. 139 p.

- [10] Stephen Pateras. IP for Embedded Diagnosis. IEEE Design and Test of Computers. 2002. P. 46-56.

- [11] V. Hahanov, V. Obrizan, V. Yeliseev, V, Ghribi. Hierachical testing of complex digital systems. Proceedings of the International Conference TCSET 2006.- Lviv, Ukraine. 2006. P. 426-429.

- [12] Avtomatizaciya diagnostirovaniya electronnyh ustroistv / Yu.V.Malyshenko i dr. / Pod. red. V.P. Chipulisa. M.:Energoatomizdat. 1986. 216 s. (In Russian)

- [13] Bennets R.Dzh. Proektirovanie testoprigodnyh logicheskih shem. Moskva. Radio i svyaz'. 1990. 175 s.

### **AUTHORS INDEX**

Adamov Alexander 122 Afanasiev I. 156 Aghababa Hossein 291 Ahmad Fuad Bader 153 Aleksanyan K. 72 Alhusein Mahmoud 467 Almaid M.K. 317 Al-Qudah Kalid 467 Al-Salaymeh Ahmed 467 Andrienko V.A. 317 Andrushchak Anatolij 179 Angelov George 311 Antonio A. de Alecrim Jr. 272 Antonova Olga 311 Austin Mick 231 Ayupov Andrey 143

Babakov R.M. 153 Babich Anna 278 Bagayev D.V. 247 Barkalov A.A. 153, 167, 171 Belkin Victor 76 Bengtsson Tomas 42 Benso A. 11 Bisikalo O.V. 440 Bodyanskiy Ye. 403 Boichuk Maryna 257 Bombieri Nicola 100 Bosio A. 11 Boule K. 149 Bulatowa Irena 420 Burachok R.A. 464 Burkatovskaya Yu. B. 355 Butorina N.B. 355 Bykova V. 327

Chaitanya Mehandru 252 Chapenko V. 149 Cheglikov Denis 126 Chekmez A.V. 453 Chemeris Alexander 423 Cho J.D. 175 Chumachenko S. 322 Chuvilo Oleg 252

Danielyan Lev 108

Demyanyshyn N. 179

Denisov Yegor 264

Devadze Sergei 241

Dimitrova-Grekow Teodora 420

Dmitrienko V.D. 428

Doroshenko Anatoliy 305

Draganov Valentin 311

Dronyuk I.M. 464

Drozd A. 461

Drozd J. 461

Eles P. 16

El-Khatib A.I. 89 Ellervee Peeter 282 Elyasi Komari Iraj 202 Engel E.A. 450 Eryar A.I. 175, 296 Evgrafov Vyacheslav 267 Evseev V.V. 472 Eyck Jentzsch 41 Fallahi Ali 217

Fedeli Andrea 116

Filaretov V.F. 184

Firuman A.C. 247

Fomina E. 327

Forouzandeh Behjat 291, 456

Foty Daniel 29

Fuchs G. 59

Fummi Franco 100

Gama Márcio 272 Gavryushenko Andiry 255 Ghazanfari Leyla S. 291 Girard P. 47 Gladkikh T.V. 428 Globa L.S. 453 Gorbenko Anatoliy 202 Gorobets O. 257 Grol V. 217 Grzes Tomasz 420 Guz Olesya 226

Haddadi Abbas 456 Hahanov Vladimir 53, 132, 226, 257, 322, 327 Hahanova A. 53 Hahanova I.V. 327 Hakobyan Sergey 108 Hammad Mahmoud 467 Handl T. 59 Hanna Laba 179 Harutunyan G. 68 Hedayatollah Bakhtari 189 Heiber Jan 59

Ivanov Andre 22 Ivanov D.E. 89 Izosimov V. 16

Jerraya Ahmed 23 Jervan Gert 282 Jutman Artur 42

Kajdan Mykola 179 Kamenuka Eugene 278 Kaminska Maryna 226 Karasyov Andrey 126 Karatkevich Andrei 112 Karavay Michail F. 24 Kascheev N. 222 Kashpur Oleg 255 Kasprowicz Dominik 301 Khadrawi A. F. 366 Kharchenko V. 190, 194, 198 Klimov A.V. 436 Klimowicz Adam 420 Klymash M.M. 464 Kołopieńczyk Małgorzata 171 Korobko Olga 344 Kot T.N. 453 Krasovskaya A. 257 Krivoulya Gennady 344 Kulak Élvira 226 Kumar Shashi 42

Ladyzhensky Y.V. 339, 385 Landrault C. 47 Lange E. 149 Leonov S.Yu. 428 Lipchansky Alexey 344 Litvinova E.I. 472 Lobachev M. 461 Lukashenko Olga 122

Majed Omar Al-Dwairi 414 Man K.L. 116 Marchenko A. 143, 156 Margarian Pavlush 140 Matrosova A.Yu. 355 Melnik D. 53 Melnikova Olga 322 Mercaldi Michele 116 Molkov Nikolay P. 348 Moraes Marlon 272 Mosin Sergey 236 Mostovaya Karina 278 Miroshnychenko Yaroslav122 Mytsyk Bohdan 179

Novák Ondřej 206 Nevludov I.Sh. 472

Obrizan Volodymyr 255 Ostanin S. 380 Ostroumov Sergii 194 Ostrovskij Igor 179

Panteleev Victor V. 443

Paolo Prinetto 11

Parfentiy Oleksandr 278

Peng Zebo 16, 42

Petrenko A.I. 239

Picolli Leonardo 272

Plotnikov Pavel V. 332

Plushch Yuri 423

Plyatsek Oleg E. 414

Podkolzin N. 264

Podyablonsky F. 222

Ponomarjova A.V. 472

Pop P. 16

Popoff Y.V. 339

Popov S. 403

Potapova K. 189

Pravadelli Graziano 100

Pravossoudovitch S. 47

Prokhorova Julia 190

Ragozin Dmitry V. 348 Rebhi A. Damseh 361 Reis Ilkka 231 Renovell Michel 482 Reza Kolahi 461 Reznikova Svetlana 423 Riznyk Oleg 335 Romankevych A. 217 Romankevych V. 189 Rousset A. 47 Rozenfeld Vladimir 163 Ruban I.V. 390 Ryabtsev V.G. 317

Saatchyan Armen 252 Safari Saeed 456 Salauyou Valery 420 Salwa Mrayyan 366 Sameh Abu-Dalo 366

Saposhnikov V.V. 287 Saposhnikov VL.V. 287 Samvel Shoukourian 39 Savino A. 11 Schellekens M.P. 116 Shannak Benbella 467 Sharshunov Sergey 76 Shevchenko Ruslan 305 Shipunov Valeriy 255 Shishkin Aleksandr V. 386 Shkil Alexandr 126 Sinelnikov V. 24 Skobelev Volodymyr 82 Skobtsov V.Y. 95 Skobtsov Y.A. 89, 95 Skvortsova Olga Smelyakov K.S. 390 Smelyakova A.S. 390 Smirnov Iouri 163 Sokolov Maxim A. 348 Sorudeykin Kirill 327 Sparks Anthony 231 Speranskiy D. 371, 436 Steininger A. 59 Sudnitson Alexander 241 Syrevitch Yevgeniya 126

Ter-Galstyan Arik 313 Teslenko G.A. 385 Titarenko Larysa, 167, 171 Tsoy Yuri R. 375 Tymochko A.I. 390

Ubar Raimund 42 Umnov Alexey L. 348 Urganskov D.I. 287 Ushakov A.A. 194

Valkovskii Vladimir 335 Vardanian Valery 68, 72 Vargas Fabian 272 Venger O. 156 Virazel A. 47

Wegrzyn A. 407, 477 Wegrzyn M. 477 Wisniewski R. 167

Yakymets Nataliya 198 Yeliseev V. 53 Yarmolik S.V. 212 Yarmolik V.N. 212 Yazik Andrey 264 Yegorov Oleksandr 264 Yeliseev V. 53 Yevtushenko N.V. 397

Zaharchenko Oleg 132 Zalyubovsky V.V. 175, 296 Zangerl F. 59 Zaychenko S. 122, 132 Zdeněk Plíva 206 Zerbino Dmitry 335 Zharikova S.V. 397 Zhereb Konstantin 305 Zhuravlev Alexander 163 Zorian Yervant 22, 39 Zuev A.V. 184