KHARKOV NATIONAL UNIVERSITY OF RADIOELECTRONICS

# Proceedings of IEEE East-West Design & Test Symposium (EWDTS'2011)

Copyright © 2011 by the Institute of Electrical and Electronics Engineers, Inc.

Technically Co-Sponsored by

tttc

Sevastopol, Ukraine, September 9 – 12, 2011

## IEEE EAST-WEST DESIGN AND TEST SYMPOSIUM 2011 ORGANISING COMMITTEE

#### **General Chairs**

V. Hahanov – Ukraine Y. Zorian – USA

#### **General Vice-Chairs**

R. Ubar – Estonia

E. Pashkov – Ukraine P. Prinetto – Italy

## Program Chairs

S. Shoukourian – Armenia D. Speranskiy – Russia

## **Program Vice-Chairs**

M. Renovell – France Z. Navabi – Iran

## Steering Committee

M. Bondarenko – Ukraine V. Hahanov – Ukraine R. Ubar – Estonia Y. Zorian – USA

### **Publicity Chairs**

G. Markosyan – Armenia S. Mosin – Russia

#### **Public Relation Chair**

V. Djigan – Russia

#### **Program Committee**

E. J. Aas – Norway J. Abraham – USA M. Adamski – Poland

- A . Barkalov Poland

- R. Bazylevych Ukraine

- A. Chaterjee USA

- V. Djigan Russia

- A. Drozd Ukraine

- E. Evdokimov Ukraine

- E. Gramatova Slovakia A. Ivanov – Canada

- M. Karavay Russia

- V. Kharchenko Ukraine

- K. Kuchukjan Armenia

- W. Kuzmicz Poland

- A. Matrosova Russia

- V. Melikyan Armenia

- L. Miklea Romania

- O. Novak Czech Republic

- Z. Peng Sweden

- A. Petrenko Ukraine

- D. Puzankov Russia

- J. Raik Estonia

- A. Romankevich Ukraine

- A. Ryjov Russia

- R. Seinauskas Lithuania

- S. Sharshunov Russia

- A. Singh USA

- J. Skobtsov Ukraine

- V. Tverdokhlebov --- Russia

- V. Vardanian Armenia

- V. Yarmolik Byelorussia

#### Organizing Committee

Yu. Gimpilevich – Ukraine S. Chumachenko – Ukraine E. Litvinova – Ukraine

## **EWDTS 2011 CONTACT INFORMATION**

Prof. Vladimir Hahanov Design Automation Department Kharkov National University of Radio Electronics, 14 Lenin ave, Kharkov, 61166, Ukraine.

Tel.: +380 (57)-702-13-26 E-mail: hahanov@kture.kharkov.ua Web: www.ewdtest.com/conf/

## 9<sup>th</sup> IEEE EAST-WEST DESIGN & TEST SYMPOSIUM (EWDTS 2011) Sevastopol, Ukraine, September 9-12, 2011

The main target of the IEEE East-West Design & Test Symposium (EWDTS) is to exchange experiences in the field of design, design automation and test of electronic circuits and systems, between the technologists and scientists from Eastern and Western Europe, as well as North America and other parts of the world. The symposium aims at attracting attendees especially from the Newly Independent States (NIS) and countries around the Black Sea and Central Asia.

We cordially invite you to participate and submit your contribution(s) to EWDTS'11 which covers (but is not limited to) the following topics:

- · Analog, Mixed-Signal and RF Test

- Analysis and Optimization

- ATPG and High-Level TPG

- · Built-In Self Test

- · Debug and Diagnosis

- · Defect/Fault Tolerance and Reliability

- Design for Testability

- Design Verification and Validation

- EDA Tools for Design and Test

- Embedded Software Performance

- · Failure Analysis, Defect and Fault

- FPGA Test

- HDL in test and test languages

- High-level Synthesis

- · High-Performance Networks and Systems on a Chip

- Low-power Design

- · Memory and Processor Test

- Modeling & Fault Simulation

- Network-on-Chip Design & Test

- · Modeling and Synthesis of Embedded Systems

- · Object-Oriented System Specification and Design

- On-Line Test

- Power Issues in Testing

- Real Time Embedded Systems

- Reliability of Digital Systems

- Scan-Based Techniques

- Self-Repair and Reconfigurable Architectures

- Signal and Information Processing in Radio and

- **Communication Engineering**

- System Level Modeling, Simulation & Test Generation

- · Using UML for Embedded System Specification

- CAD Session:

- CAD and EDA Tools, Methods and Algorithms

- Design and Process Engineering

- · Logic, Schematic and System Synthesis

- Place and Route

- Thermal, Timing and Electrostatic Analysis of SoCs and Systems on Board

- Wireless Systems Synthesis

- Digital Satellite Television

The EWDTS'2011 will take place in Sevastopol, Ukraine. Sevastopol is a port city, located on the Black Sea coast of the Crimea peninsula. The city, formerly the home of the Soviet Black Sea Fleet, is now home to a Ukrainian naval base and facilities leased by the Russian Navy and used as the headquarters of both the Ukrainian Naval Forces and Russia's Black Sea Fleet.

The symposium is organized by Kharkov National University of Radio Electronics in cooperation with Sevastopol National Technical University and Tallinn University of Technology. It is technically cosponsored by the IEEE Computer Society Test Technology Technical Council (TTTC) and financially supported by Virage Logic, Synopsys, Aldec, Kaspersky Lab, DataArt Lab, Tallinn Technical University, Cadence.

Accelerating Silicon Success

DEC

## CONTENTS

| Automated Test Bench Generation for High-Level Synthesis flow ABELITE<br>Taavi Viilukas, Maksim Jenihhin, Jaan Raik, Raimund Ubar, Samary Baranov1                     | 3 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

| About Dependability in Cyber-Physical Systems<br>Liviu Miclea, Teodora Sanislav1                                                                                       | 7 |

| Self-healing Capabilities through Wireless Reconfiguration of FPGAs<br>George Dan Moiş, Mihai Hulea, Silviu Folea and Liviu Miclea                                     | 2 |

| Software Testing of a Simple Network<br>Jack H. Arabian                                                                                                                | 8 |

| A New Core to Monitor RTOS Activity in Embedded Systems<br>Dhiego Silva, Letícia Bolzani, Fabian Vargas                                                                | 2 |

| A unifying formalism to support automated synthesis of SBSTs for embedded caches<br>Stefano Di Carlo, Giulio Gambardella, Marco Indaco, Daniele Rolfo, Paolo Prinetto  | 9 |

| Simulation-Based Hardware Verification with Time-Abstract Models Alexander Kamkin                                                                                      | 3 |

| Programmable Current Biasing for Low Noise Voltage Controlled Oscillators<br>Vazgen Melikyan, Armen Durgaryan4                                                         | 7 |

| Adaptive Signal Processing in Multi-Beam Arrays<br>Victor I. Djigan                                                                                                    | 1 |

| Optimization of Microprogram Control Unit with Code Sharing<br>A. Barkalov, L.Titarenko, L.Smolinski                                                                   | 5 |

| Synthesis of control unit with refined state encoding for CPLD devices<br>A.Barkalov, L.Titarenko, S.Chmielewski                                                       | 0 |

| Cybercomputer for Information Space Analysis<br>Vladimir Hahanov, Wajeb Gharibi, Dong Won Park, Eugenia Litvinova                                                      | 6 |

| Verification and Diagnosis of SoC HDL-code<br>Vladimir Hahanov, Dong Won Park, Olesya Guz, Sergey Galagan, Aleksey Priymak72                                           | 2 |

| Diagnosis Infrastructure of Software-Hardware Systems<br>Tiecoura Yves, Vladimir Hahanov, Omar Alnahhal, Mikhail Maksimov,<br>Dmitry Shcherbin, Dmitry Yudin           | 4 |

| Overview of the Prototyping Technologies for Actel® RTAX-S FPGAs Olga Melnikova                                                                                        | 0 |

| Hardware Reduction for Matrix Circuit of Control Moore Automaton<br>A. Barkalov, L.Titarenko, O. Hebda                                                                 | 4 |

| RoCoCo: Row and Column Compression for High-Performance Multiplication on FPGAs<br>Fatih Ugurdag, Okan Keskin, Cihan Tunc, Fatih Temizkan, Gurbey Fici, Soner Dedeoglu | 8 |

| Test Architecture Design for TSV based 3D Stacked ICs using Hard SOCs<br>Surajit K. Roy, Chandan Giri, Arnab Chakraborty, Subhro Mukherjee,<br>Debesh K. Das and Hafizur Rahaman                          | . 102 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| Efficient selective compaction and un-compaction of inconsequential logical design units in the schematic representation of a design <b>Tarun Kumar Goyal, Amarpal Singh, Rahul Aggarwal</b>              | 106   |

| Quasioptimal Algorithm of Carrier Recovery in Coherent Receiver<br>of M-ary Alphabets APK-Signals without Traditional PLL<br>Victor V. Panteleev                                                          | 112   |

| Quasioptimal Algorithm of Timing Recovery in Autocorrelation Receiver of Phase Shift Keying Signal<br>Vitaliy A. Balashov, Victor V. Panteleev, Leonid M. Lyakhovetskyy                                   |       |

| Design of Microprogrammed Controllers with Address Converter implemented on<br>Programmable Systems with Embedded Memories<br>Remigiusz Wiśniewski, Monika Wiśniewska, Marek Węgrzyn, Norian Marranghello | 123   |

| Reduction of the Memory Size in the Microprogrammed Controllers<br>Monika Wiśniewska, Remigiusz Wiśniewski, Marek Węgrzyn, Norian Marranghello                                                            | . 127 |

| Maintaining Uniformity in the Processes of Encryption and Decryption with a Variable Number of Encryption Rounds<br>L. Smolinski                                                                          | 131   |

| C++TESK-SystemVerilog United Approach to Simulation-Based Verification of Hardware Designs<br>Mikhail Chupilko                                                                                            | . 136 |

| Advanced Scan Chain Configuration Method for Broadcast Decompressor Architecture<br>Jiří Jeníček and Ondřej Novák, Martin Chloupek                                                                        | . 140 |

| A Programmable BIST with Macro and Micro codes for Embedded SRAMs<br>P. Manikandan, Bjørn B Larsen, Einar J Aas, Mohammad Areef                                                                           | . 144 |

| Modified Protocol for Data Transmission in Ad-Hoc Networks with High<br>Speed Objects Using Directional Antennas<br>Victor Barinov, Alexey Smirnov, Danila Migalin                                        | 150   |

| High Performance Audio Processing SoC Platform<br>Denis Muratov, Vladimir Boykov, Yuri Iskiv, Igor Smirnov, Sergey Berdyshev, Valeriy Vertegel,<br>Yuri Gimpilevich, Gilad Keren                          |       |

| Methodology of the Pre-silicon Verification of the Processor Core<br>Sergii Berdyshev, Vladimir Boykov, Yuri Gimpilevich, Yuri Iskiv, Gilad Keren,<br>Denis Muratov, Igor Smirnov, Valeriy Vertegel       | 158   |

| Spam Diagnosis Infrastructure for Individual Cyberspace<br>Vladimir Hahanov, Aleksandr Mischenko, Svetlana Chumachenko, Anna Hahanova,<br>Alexey Priymak                                                  | 161   |

| A Security Model of Individual Cyberspace<br>Alexander Adamov, Vladimir Hahanov                                                                                                                           | 169   |

| Organization of Pipeline Operations in Mapping Unit of the Dataflow Parallel Computing System<br>Levchenko N.N., Okunev A.S, Yakhontov D.E                                                                               |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A Subsystem for Automated Synthesis of LFSR-Based Test Generator for Deterministic and Pseudorandom Testing Sergey G. Mosin, Natalia V. Chebykina, Maria S. Serina                                                       |

| Sergey G. Mosili, Natalia V. Chebykilla, Maria S. Serilla                                                                                                                                                                |

| Debugging and testing features of the dataflow parallel computing system components and devices Levchenko N.N., Okunev A.S., Yakhontov D.E., Zmejev D.N                                                                  |

| Adaptive Wavelet Codec for Noisy Image Compression<br>Yuri S. Bekhtin                                                                                                                                                    |

| TCAD-SPICE simulation of MOSFET switch delay time for different CMOS technologies<br>K. O. Petrosyants, E. V. Orekhov, D. A. Popov, I. A. Kharitonov, L. M. Sambursky,<br>A. P. Yatmanov, A. V. Voevodin, A. N. Mansurov |

| Design Fault Injection-Based Technique and Tool for FPGA Projects Verification<br>L. Reva , V. Kulanov, V. Kharchenko                                                                                                    |

| Optimal Schematic Design of Low-Q IP Blocks<br>Sergey G. Krutchinsky, Mikhail S. Tsybin                                                                                                                                  |

| Parallelizing of Boolean function system for device simulation<br>Alexander Chemeris, Svetlana Reznikova                                                                                                                 |

| Optimization Some Characteristics of Continuous Phase Spread Spectrum Signal<br>Michael Balanov, Olga Mamedova                                                                                                           |

| Development Methodology of Interoperable Add-on Tool for Static Verification of Current Density<br>E. Babayan                                                                                                            |

| Design Consideration of CMOS Low Cut-Off Low Pass Filter for ECG Applications<br>Andranik Hovhannisyan                                                                                                                   |

| Method of Capacitor Calibration for Switched Capacitor Circuits<br>Norayr K. Aslanyan                                                                                                                                    |

| Built-in Measurement Technique for On-Chip Capacitors<br>Andranik S Hovhannisyan, Norayr K Aslanyan, Vahram K Aharonyan, Hayk H Dingchyan                                                                                |

| A Generation of Canonical Forms for Design of IIR Digital Filters<br>Vladislav A. Lesnikov, Alexander V. Chastikov, Tatiana V. Naumovich, Sergey V. Armishev 221                                                         |

| Variant of Wireless MIMO Channel Security Estimation Model Based on Cluster Approach<br>O. Kuznietsov, O. Tsopa                                                                                                          |

| Compact DSM MOSFET Model and its Parameters Extraction<br>Anatoly Belous, Vladislav Nelayev, Sergey Shvedov, Viktor Stempitsky,<br>Tran Tuan Trung, Arkady Turtsevich                                                    |

| IGBT Technology Design and Device Optimization<br>Artem Artamonov, Vladislav Nelayev, Ibrahim Shelibak, Arkady Turtsevich                                                                                                |

| Device-Process Simulation of Discrete Silicon Stabilitron with the Stabilizing Voltage of 6,5 V<br>Dudar N.L., Borzdov V.M.                                                                          | . 237 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| Geometrical Approach to Technical Diagnosing of Automatons<br>Tverdokhlebov V.A.                                                                                                                     | . 240 |

| Loop Fusion and Power Consumption of PCs Dmytro Lazorenko                                                                                                                                            | .244  |

| On Experimental Research of Efficiency of Tests Construction for Combinational Circuits by the Focused Search Method <b>Vasily Kulikov, Vladimir Mokhor</b>                                          | . 247 |

| Test Set Compaction Procedure for Combinational Circuits Based On Decomposition Tree Valentina Andreeva                                                                                              | . 251 |

| Implementation by the Special Formula of an Arbitrary Subset of Code Words of ( <i>m</i> , <i>n</i> )-code for Designing a Self-Testing Checker<br><b>N. Butorina, S. Ostanin</b>                    | . 255 |

| Optimal Fluctuations for Satisfactory Performance under Parameter Uncertainty<br>HJ Kadim                                                                                                            | . 259 |

| The Evidential Independent Verification of Software of Information and<br>Control Systems, Critical to Safety: Functional Model of Scenario<br>Konorev Borys, Sergiyenko Volodymyr, Chertkov Georgiy | . 263 |

| Si BJT and SiGe HBT Performance Modeling after Neutron Radiation Exposure<br>Konstantin Petrosyants, Eric Vologdin, Dmitry Smirnov, Rostislav Torgovnikov,<br>Maxim Kozhukhov                        | . 267 |

| Compact Power BJT and MOSFET Models Parameter Extraction with Account for Thermal Effects<br>I. A. Kharitonov                                                                                        | . 271 |

| Thermal Analysis of the Ball Grid Array Packages<br>K.O. Petrosyants, N.I. Rjabov                                                                                                                    | . 275 |

| On Synthesis of Degradation Aware Circuits at Higher Level of Abstraction<br>Mohammad Abdul Razzaq, Alok Baluni, Virendra Singh,<br>Ram Rakesh Jangiry and Masahiro Fujitaz                          | . 279 |

| Selection of the State Variables for Partial Enhanced Scan Techniques<br>A. Matrosova, A. Melnikov, R. Mukhamedov, V. Singh                                                                          | . 285 |

| Efficient Regular Expression Pattern Matching using Cascaded Automata Architecture for Network Intrusion Detection Systems<br>Pawan Kumar and Virendra Singh                                         | . 290 |

| Dispersion Analysis in Processes of Passive Monitoring and Diagnosing of Enterprise Area Networks Anna V. Babich, Murad Ali A.                                                                       | . 295 |

| A Diagnostic Model for Detecting Functional Violation in HDL-Code of System-on-Chip<br>Ngene Christopher Umerah, Vladimir Hahanov                                                                    | . 299 |

| Competence as a Support Factor of the Computer System Operation<br>Krivoulya G., Shkil A., Kucherenko D                                                                          |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A Model of Spatial Thinking for Computational Intelligence<br>Kirill A. Sorudeykin                                                                                               |

| New Methods and Tools for Design of Tests Memory<br>Mudar Almadi, Diaa Moamar, Vladimir Ryabtsev                                                                                 |

| Scalability of "Ideal" System Networks Based on Quasy-Complete Graph Architecture<br>Mikhail F. Karavay and Victor S. Podlazov                                                   |

| The Test Method for Identification of Radiofrequency Wireless Communication Channels Using Volterra<br>Model<br>Vitaliy D. Pavlenko, Viktor O. Speranskyy, Vladimir I. Lomovoy   |

| A Calculation of Parasitic Signal Components Digital Filtration for the Retransmission Meter on the basis of FPGA                                                                |

| Velichko D.A., Vdovychenko I.I                                                                                                                                                   |

| The Testware CAD<br>Victor Zviagin                                                                                                                                               |

| The Synthesis of Periodic Sequences with Given Correlation Properties<br>V. M. Koshevyy, D. O. Dolzhenko                                                                         |

| Lyapunov Function Analysis for Different Strategies of Circuit Optimization<br>A. Zemliak, A. Michua, T. Markina                                                                 |

| State Identification of Bilinear Digital System<br>Dmitriy Speranskiy                                                                                                            |

| Model order reduction of Micro-Electro-Mechanical Systems Petrenko Anatoly                                                                                                       |

| Modeling a Logical Network of Relations of Semantic Items in Superphrasal Unities<br>Nina Khairova, Natalia Sharonova                                                            |

| Resistance Dependent Delay Behavior of Resistive Open Faultsin Multi Voltage Designs Environment<br>Mohamed Tag Elsir Mohammadat, Noohul Basheer Zain Ali, Fawnizu Azmadi Hussin |

| Designing ISA Card with Easy Interface<br>Taghi Mohamadi                                                                                                                         |

| Real Time Operating System for AVR Microcontrollers<br>Taghi Mohamadi                                                                                                            |

| Recognition of Automatons by their Geometrical Images<br>Epifanov A.S                                                                                                            |

| Problems of Cause-Effect Link's Definition in Man-Machine Systems' Accidents<br>Rezchikov A.F                                                                                    |

| OFDM-based Audio Watermarking for Covered Data Transmission in VHF Radiotelephony<br>Oleksandr V. Shishkin, Oleksandr O. Lyashko                         | 389 |

|----------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Validation&Verification of an EDA Automated Synthesis Tool<br>Giulio Gambardella, Marco Indaco, Paolo Prinetto, Daniele Rolfo                            | 393 |

| Infrastructure for Testing and Diagnosing Multimedia Device<br>Vladimir Hahanov, Karyna Mostova, Oleksandr Paschenko                                     | 394 |

| Architecture for an Intelligent Test Error Detection Agent<br>Matthias Kirmse, Uwe Petersohn, Elief Paffrath                                             | 400 |

| Cadence EDA Flow for IC's and Electronics<br>Anatoli Ivanov                                                                                              | 405 |

| Designing an Embedded System for Interfacing with Networks Based on ARM<br>Taghi Mohamadi                                                                | 407 |

| Checkability of the Digital Components in Safety-Critical Systems: Problems and Solutions<br>A. Drozd, V. Kharchenko, S. Antoshchuk, J. Sulima, M. Drozd | 411 |

| AUTHORS INDEX                                                                                                                                            | 416 |

## **Diagnosis Infrastructure of Software-Hardware Systems**

Tiecoura Yves (Cote d'Ivoire)<sup>1</sup>, Vladimir Hahanov<sup>1</sup>, Omar Alnahhal (Livan)<sup>1</sup>, M. Maksimov<sup>1</sup>, Dmitry Shcherbin<sup>1</sup>, Dmitry Yudin<sup>1</sup>

<sup>1</sup> Computer Engineering Faculty, Kharkov National University of Radioelectronics, Kharkov, Ukraine, hahanov@kture.kharkov.ua

#### Abstract

This article describes an infrastructure and technologies for diagnosis. A transactional graph model and method for diagnosis of digital system-on-chip are developed. They are focused to considerable decrease the time of fault detection and memory for storage of diagnosis matrix by means of forming ternary relations in the form of test, monitor, and functional component. The following problems are solved: creation of digital system model in the form of transaction graph and multitree of fault detection tables, as well as ternary matrices for activating functional components in tests, relative to the selected set of monitors; development of a method for analyzing the activation matrix to detect the faults with given depth and synthesizing logic functions for subsequent embedded hardware fault diagnosing.

## 1. TAB-model for diagnosing faulty components of SoC

Motivation is determined by the following: 1) the creation of simple and applicable models, methods and engines for diagnosis of multilayer software and hardware systems; 2) market appeal of matrix or table method for fault detection of SoC components (hardware and software) as the most effective one, which is focused on parallel processing and makes it possible to considerably reduce the time of diagnosis in the event of faults or non-functional mode.

Aim of this article is creation of model and method for considerable decrease the time of testing and memory for storage of diagnosis matrix by means of forming ternary relations (test - monitor - functional component) in a single table TAB: Tests - Assertions -Blocks. The problems are: 1) development of digital system model in the form of transaction graph, as well as multi-level model and engine for diagnosing software and hardware modules, based on the use of activation matrix of functional components on the tests relative to the selected monitor set [1-6]; 2) development of a method for analyzing activation matrix to detect faults with a given depth [4-7]; 3) Synthesis of logic functions for embedded fault diagnosis [8-11].

Model for testing a digital system is represented by the following transformation of the initial diagnosis equation, defined by xor-relation of the parameters <test functionality - faulty blocks>:

$$T \oplus F \oplus B = 0 \rightarrow B = T \oplus F \rightarrow B = \{T \times A\} \oplus F \rightarrow B = \{T \times A\} \oplus \{F \times m\}$$

which is transformed in ternary matrix relation of the components:

$$\mathbf{M} = \{\{\mathbf{T} \times \mathbf{A}\} \times \{\mathbf{B}\}\} \leftarrow \mathbf{M}_{ij} = (\mathbf{T} \times \mathbf{A})_i \oplus \mathbf{B}_j.$$

Here, the coordinate of matrix (table) is equal to 1, if the pair test-monitor  $(T \times A)_i$  checks (activates) faults of the functional block  $B_i \in B$ .

A model of digital system is presented in the transaction graph:

$$G = \langle B, A \rangle, B = \{B_1, B_2, ..., B_i, ..., B_n\},\$$

$A = \{A_1, A_2, ..., A_{i}, ..., A_m\}$

where sets of arcs - functional blocks and nodes monitors for observation of the digital system variables are defined.

For diagnosing a set of test segments  $T = {T_1, T_2, ..., T_r, ..., T_k}$  is overlapped on the graph model, which activates the transaction paths in the graph. In general, the testing model is represented by the Cartesian product  $M = \langle B \times A \times T \rangle$  that has the dimension  $O = n \times m \times k$ . To reduce the amount of diagnostic information it is offered to assign a monitor to each test, which answers for visualization of an activation way for functional blocks, which makes it possible to decrease the dimension of model (matrix) to  $Q = n \times k$  and retain all features of the triad relationship  $M = \langle B \times A \times T \rangle$ . For the pair «test – monitor» not only one-to-one correspondence is possible  $\langle T_i \rightarrow A_i \rangle$ , but functional  $\langle \{T_i, T_r\} \rightarrow A_i \rangle$  and

injective ones  $\langle T_i \rightarrow \{A_j, A_s\} \rangle$ . Such variety of correspondences makes it possible to duplicate one test segment for different monitors, as well as assign several tests to the same monitor. At that the matrix cell  $M_{ii} = \{0,1\}$  always preserves its dimension, equal to 1 bit.

The analytical generalized model for matrix diagnosing by using monitor engine, focused to achieving a given depth of fault detection, is presented in the following form:

$$\begin{split} &M = f(G,L,T,B,A,t), \\ &B = \{B_1,B_2,...,B_i,...,B_m\}; \\ &L = \{L_1,L_2,...,L_i,...,L_n\}; \\ &A(t) = \{A_1,A_2,...,A_i,...,A_k\}; \\ &A \subseteq L; \ G = L \times B; \ k \leq n; \\ &T = \{T_1,T_2,...,T_i,...,T_p\}. \end{split}$$

Here B<sub>i</sub> is a group of code statements, assigned to the node L<sub>i</sub> (variable, register, counter, memory), determining its state; G is functionality, presented by the transaction graph  $G = (L, A) \times B$  in the form of the Cartesian product of node and arc sets; A is a set of monitors, as a subset of transaction graph nodes  $A \subseteq L$ . The method for detecting faults of the functional blocks (FB) uses pre-built activation table (matrix) ATFB  $M = [M_{ij}]$ , where row is the relation be-

tween the test segment and a subset of activated blocks  $\mathbf{T} \rightarrow \mathbf{A} \quad (\mathbf{M} \quad \mathbf{M} \quad \mathbf{M} \quad \mathbf{M} \rightarrow \mathbf{M} \quad (0.1)$

$$I_i \to A_j \approx (M_{i1}, M_{i2}, ..., M_{ij}, ..., M_{in}), M_{ij} = \{0, 1\},\$$

observed on the monitor Ai. Column of the table describes the relation between the functional block, test segments and monitors  $M_i = B_i \approx f(T, A)$ . In the monitor engine the simulated time can be introduced, which complicates the activation matrix, indicating real or simulated cycle, on which monitoring of the node or functional block states on the test segment  $A_i = f(T_i, B_i, t_i)$  is performed.

For fault diagnosis at the modeling stage the generalized response (column vector)  $m = \{m_1, m_2, ..., m_i, ..., m_p\}$  of monitor engine A on the test segments T is determined, by forming  $m_i = f(T_i, A_i)$ . Searching faulty functional blocks is based on the definition of xor-operation between the assertion state vector and columns of the functional failures table  $m \oplus (M_1 \lor M_2 \lor ... \lor M_j \lor ... \lor M_n)$ . The choice of solution is realized by using a method for xor-analyzing columns, to choose a set of vectors B<sub>1</sub> with minimum number of unit coordinates:

$$B = \min_{j=1,n} \left[ B_j = \sum_{i=1}^p (B_{ij} \bigoplus_{i=1}^p m_i) \right],$$

forming the functional blocks with faults, verified on the test segments. In addition to the model for matrix diagnosing is necessary to describe the following important features of the matrix:

$$\begin{split} 1) & M_{i} = (T_{i} - A_{j}); \\ 2) & \stackrel{m}{\lor} M_{ij} \rightarrow \forall M_{j} = 1; \\ 3) & M_{ij} \stackrel{n}{\oplus} M_{rj} \neq M_{ij}; \\ 4) & M_{ij} \stackrel{k}{\oplus} M_{ir} \neq M_{ij}; \\ 5) & \log_{2} n \leq k \leftrightarrow \log_{2} |B| \leq |T| \\ 6) & B_{j} = f(T, A) \rightarrow B \oplus T \oplus A = 0. \end{split}$$

The features means: 1) Each row of the matrix is a match or subset of the Cartesian product (test - monitor). 2) Disjunction of all rows of the matrix gives a vector equal to one over all the coordinates. 3) All rows are distinct, which eliminates the test redundancy. 4) All columns of the matrix are distinct, which exclude the existence of equivalent faults. 5) The number of matrix rows must be greater than the binary logarithm of the number of columns that determines the potential diagnosability of all blocks. 6) Diagnosis function for block depends on the complete test and monitors, which must be minimized without reduction the diagnosability.

### 2. Design diagnosability

As for the quality of the model for diagnosing functional failures, it shows the efficiency of the use of pair (test, assertions) for a given diagnosis depth. Evaluation of the model quality is functionally dependent on the length of the test |T|, a number of assertions |A|, and a number of detected blocks with functional failures N<sub>d</sub> on the total number of software blocks N:

$$\mathbf{Q} = \mathbf{E} \times \mathbf{D} = \frac{]\log_2 \mathbf{N}[}{|\mathbf{T}| \times |\mathbf{A}|} \times \frac{\mathbf{N}_d}{\mathbf{N}} .$$

The diagnosis efficiency is the ratio of the minimum number of bits needed for identification (recognition) of all the blocks to the real number of code bits, presented by the product of test length by number of assertions in each of them. If the first fraction of estimate is equal to 1 and all the blocks with functional failures

are detected ( $N_d = N$ ), it means a test and assertions are optimal that gives value of 1 for quality criterion of diagnosis model.

Evaluation of the structure quality for the design code is interesting from the perspective of the diagnosability of software blocks. The purpose of the analysis is determining the quantitative assessment of the graph structure and a node for placement of assertion monitors, which make possible to obtain maximum diagnosis depth of functional failures of the software components. It is important not controllability and observability as in testability, but the distinguishability of the software components with functional failures, in the limit it is zero blocks with the equivalent (indistinguishable) failures. Such an assessment may be useful to compare the graphs implemented the same functionality. It is necessary to evaluate the graph structure from the position of potential detection depth of software functional failures. One possible option is diagnosability of ABC-graph as a function depending on adjacent arcs of each node (the number Nn), one of which is incoming, other one is outgoing. These arcs form paths without reconvergent fan-outs and branching (N is total number of arcs in the graph):

$$D = \frac{N - N_n}{N}$$

Each node, joining two arcs entering in the number  $N_n$ , is called transit one. The estimation  $N_n$  is the number of indistinguishable functional failures of the software components. Potential locations of monitors for distinguishing functional failures are transit nodes. Given the above estimation of the diagnosability D the diagnosis model quality for software takes the form:

$$Q = E \times D = \frac{]log_2N[}{|T| \times |A|} \times \frac{N - N_n}{N}$$

Rules for synthesis of diagnosable software: 1) Test (testbench) must create minimum number of onedimensional activation paths, covered all the nodes and arcs of ABC-graph. 2) The base number of monitorassertions equals the number of end nodes of the graph with no outgoing arcs. 3) An additional monitor can be placed in each node, which has one incoming and one outgoing arc. 4) Parallel independent code blocks have n monitors and a single test or one integrated monitor and n tests. 5) Serially connected blocks have one activation test for serial path and n-1 monitor or n tests and n monitors. 6) The graph nodes, which have different numbers of input and output arcs, create the conditions for the diagnosability of current section by onedimensional activation tests without having to install additional monitors. 7) The set of test segments (testbench) has to be 100% functional coverage, given by the nodes of ABC-graph. 8) Diagnozability function is directly proportional to the test length, the number of assertions and inversely proportional to the binary logarithm of the number of software blocks:

$$D = \frac{N - N_n}{N} = f(T, A, N) = \frac{|T| \times |A|}{]log_2 N[}$$

Diagnosability as a function depending on the graph structure (for software), test and assertion monitors can always be reduced to unit value. For this purpose there are two alternative ways. The first one is increase of test segments, activating new paths for distinguishing equivalent faults without increasing assertions, if the software graph structure allows the potential links. The second is placement of additional assertion monitors in transit nodes of the graph. A third hybrid variant is possible, based on the joint application of two above ways. The relation of three components (the number of software blocks, the power of assertion engine and the test length) forms the set of optimal solutions

$$D = 1 \rightarrow \frac{|T| \times |A|}{]\log_2 N[} = 1 \rightarrow ]\log_2 N[= |T| \times |A|,$$

when quality of the diagnosis and diagnosability model is equal to 1. It can be useful for choosing an quasioptimal variant of alternative way for providing the full distinguishability of software functional failures on a pair  $|T| \times |A|$ .

## 3. Multilevel method (engine) for diagnosis of digital system

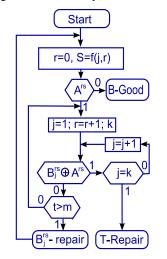

Process model or method for searching faults by diagnosis multitree is reduced to creation of the engine (Fig. 1) for traversal of tree branch on the depth, specified by the user:

$$B_j^{rs} \oplus A^{rs} = \begin{cases} 0 \to \{B_j^{r+1,s}, R\}; \\ 1 \to \{B_{j+1,s}^{rs}, T\}. \end{cases}$$

Here vector xor-operation is executed between the columns of the matrix and the output response vector  $A^{rs}$ , which is determined by the functionality response taken from the monitors (assertions or bits of boundary scan register) under all test patterns. If at least one coordinate of vector xor-sum is equal to zero  $B_1^{rs} \oplus A^{rs} = 0$  then one of the following action is performed: the transition to the activation matrix of lower level  $B_j^{r+1,s}$  or repair of the functional block  $B_j^{rs}$ . At that analysis is carried out, what is the most important: 1) time – then repair of faulty block is performed; 2) money – then a transition down is carried out to specify the fault location, because replacement of smaller block substantially decreases the repair cost. If at least one coordinate of the resulting xor-sum vector is equal to one  $B_j^{rs} \oplus A^{rs} = 1$ , then transition to the next matrix column is performed. When all coordinates of the assertion monitor vector are equal to zero  $A^{rs} = 0$ , faultfree state of a device is fixed. If all vector sums are not equal to zero  $B_j^{rs} \oplus A^{rs} = 1$ , it means a test, generated for check the given functionality, has to be corrected.

Fig. 1. Engine for traversal of diagnosis multitree

Thus, the graph shown in the Fig. 1, allows realizing efficient infrastructure IP for complex technical systems. The advantages of the engine, which is invariant to the hierarchy levels, are the simplicity of preparation and presentation of diagnostic information in the form of minimizing activation table of functional blocks on the test patterns.

## 4. Verification of models and method for diagnosis

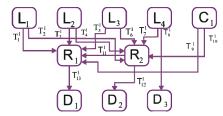

To illustrate the performance of the proposed model and method the functionalities of three modules

of the digital filter of Daubechies [11] are considered below. The first component is component Row\_buffer; its transaction graph, based on RTL-model, shown in Fig. 2. Nodes are presented by the states of variables and monitors, which are responsible for node incoming transactions or arcs, corresponding to the functional blocks.

## Fig. 2. Component Row\_buffer of transaction graph

An activation table for functional blocks is generated by using graph, obtained in the simulation. Table rows are activation paths for blocks to the given monitornode. A table is a coverage all columns or functional blocks by rows of paths. In this case it should not have at least two identical columns. The difference of table is creation of the pair <test – observed node>, making it possible to considerably reduce the dimension of the table with 100% detection of all faulty blocks. The main feature of the proposed model is the ability to describe the following relations by using the table: distinct tests – one node, one test – distinct nodes:

| A <sub>ij</sub>          | T <sub>1</sub> | Т2 | T <sub>3</sub> | T <sub>4</sub> | T <sub>5</sub> | T <sub>6</sub> | T <sub>7</sub> | T <sub>8</sub> | T9 | T <sub>10</sub> | T <sub>11</sub> | T <sub>12</sub> | T <sub>13</sub> |

|--------------------------|----------------|----|----------------|----------------|----------------|----------------|----------------|----------------|----|-----------------|-----------------|-----------------|-----------------|

| $t_1 \rightarrow D_3$    |                |    |                |                |                |                |                | 1              |    |                 |                 |                 |                 |

| $t_2 \rightarrow D_1$    | 1              |    |                | -              |                |                |                |                |    |                 | -               |                 | 1               |

| $t_3 \rightarrow D_1$    |                |    | 1              | -              |                |                |                |                |    |                 |                 |                 | 1               |

| $t_4 \rightarrow D_1$    |                |    |                |                | 1              |                |                |                |    |                 | -               |                 | 1               |

| $t_5 \rightarrow D_1$    |                |    |                | -              |                |                |                |                |    |                 | 1               |                 | 1               |

| $t_6 \rightarrow D_1$    |                |    |                |                |                |                |                |                | 1  |                 |                 |                 | 1               |

| $t_7 \rightarrow D_2$    |                | 1  |                | -              |                |                |                |                |    |                 |                 | 1               | .               |

| $t_8 \rightarrow D_2$    |                |    |                | 1              |                |                |                |                |    |                 |                 | 1               | .               |

| $t_9 \rightarrow D_2$    |                |    |                |                |                | 1              |                |                |    |                 |                 | 1               | .               |

| $t_{10} \rightarrow D_2$ |                |    |                |                |                |                | 1              |                |    |                 |                 | 1               | .               |

| $t_{11} \rightarrow D_2$ |                |    |                |                |                |                |                |                |    | 1               |                 | 1               |                 |

The use of the activation matrix of functional blocks (transaction graph) and xor-method for detecting faults allows synthesizing logic functions for the combination circuit, which determines number of functional block with semantic errors in process of simulation:

$$\begin{split} D_3 &= T_8^1;\\ D_1 &= T_{13}^1 T_1^1 \vee T_{13}^1 T_3^1 \vee T_{13}^1 T_5^1 \vee T_{13}^1 T_{11}^1 \vee T_{13}^1 T_9^1;\\ D_2 &= T_{12}^1 T_2^1 \vee T_{12}^1 T_4^1 \vee T_{12}^1 T_6^1 \vee T_{12}^1 T_7^1 \vee T_{12}^1 T_{10}^1. \end{split}$$

This feature is possible due to the lack of equivalent faults or identical columns in the activation

matrix. Therefore, fixing the actual state of monitors at the nodes  $D_1, D_2, D_3$  on 11 test patterns makes it possible to unambiguously identify an incorrect functional module by performing xor-operation between the assertion vector and the columns of activation matrix. Zero value of all the coordinates for the result of xor-operations determines the number of the column corresponding to a faulty module. The implementation of the model and method in a logical function allows identifying the faulty block before the completion of the diagnostic experiment, if it is possible. This means significant savings of diagnosis time for certain types of faults. For instance, the testmonitor  $t_1 \rightarrow D_3$  allows identifying a fault of the block B<sub>8</sub> at the first test.

Second test case for the practical use of the activation model and xor-method for searching faults is presented below. Synthesis of the diagnosis matrix for discrete cosine transform module from Xilinx library in the form of functional coverage is shown in Listing 1.

Listing 1. Part of functional coverage c0: coverpoint xin bins minus big={[128:235]}; bins minus\_sm={[236:255]}; bins plus\_big={[21:127]}; bins plus\_sm={[1:20]}; bins zero={0}; c1: coverpoint dct\_2d bins minus\_big={[128:235]}; bins minus\_sm={[236:255]}; bins plus\_big={[21:127]}; bins plus\_sm={[1:20]}; bins zero={0}; bins zero2=(0=>0); } endaroup

For all 12 modules the transaction graphs, activation tables, and logic functions are developed for testing and fault detection in the discrete cosine transform. Graph with the activation matrix and logic function (Fig. 3) are presented below.

This graph is associated with the following diagnosis matrix:

| A <sub>ij</sub>          | T <sub>1</sub> | T2 | T <sub>3</sub> | T <sub>4</sub> | T <sub>5</sub> | T <sub>6</sub> | T <sub>7</sub> | T <sub>8</sub> | T9 | T <sub>10</sub> | T <sub>11</sub> | T12 | T13 | $T_{14}$ |

|--------------------------|----------------|----|----------------|----------------|----------------|----------------|----------------|----------------|----|-----------------|-----------------|-----|-----|----------|

| $P_1 \rightarrow F_7$    | 1              |    | 1              |                | 1              | -              | 1              | -              |    |                 |                 |     |     |          |

| $P_2 \rightarrow F_8$    |                | 1  |                | 1              | 1              | -              |                | 1              |    |                 |                 |     |     |          |

| $P_3 \rightarrow F_9$    | 1              | -  | 1              |                | -              | 1              | -              |                |    |                 | 1               |     |     |          |

| $P_4 \rightarrow F_{10}$ |                | 1  |                | 1              |                | 1              |                |                |    |                 |                 | 1   |     |          |

| $P_5 \rightarrow F_{12}$ | 1              | -  | 1              |                | 1              | -              | -              |                | 1  |                 |                 |     | 1   |          |

| $P_6 \rightarrow F_{13}$ |                | 1  |                | 1              |                | 1              |                |                |    | 1               |                 |     |     | 1        |

| $P_1 \rightarrow F_2$    | 1              | -  |                |                |                | -              | -              |                |    |                 |                 |     |     |          |

| $P_2 \rightarrow F_3$    | .              | 1  |                |                | -              | -              |                |                |    |                 |                 |     |     |          |

The system of diagnosis functions is presented below:

$$F_{7} = T_{1}^{1}T_{3}^{1}T_{5}^{1}T_{7}^{1}; F_{8} = T_{2}^{1}T_{4}^{1}T_{5}^{1}T_{8}^{1};$$

$$F_{9} = T_{11}^{1}T_{6}^{1}T_{1}^{1}T_{3}^{1};$$

$$F_{10} = T_{4}^{1}T_{5}^{1}T_{6}^{1}T_{12}^{1}; F_{12} = T_{1}^{1}T_{3}^{1}T_{5}^{1}T_{9}^{1}T_{13}^{1};$$

$$F_{13} = T_{2}^{1}T_{4}^{1}T_{6}^{1}T_{10}^{1}T_{14}^{1};$$

$$F_{2} = T_{1}^{1}; F_{3} = T_{2}^{1};$$

$$T_{3}^{1} \qquad F_{3} = T_{2}^{1};$$

$$T_{5}^{1} \qquad F_{4} \qquad T_{6}^{1} \qquad T_{12}^{1};$$

$$F_{7} \qquad F_{8} \qquad F_{13} \qquad T_{10}^{1} \qquad F_{6} \qquad T_{12}^{1};$$

$$F_{13} = T_{12}^{1}T_{13}^{1} \qquad F_{10} \qquad F_{10}^{1};$$

### Fig. 3. Transaction graph of main-RTL module

Fragment of monitor engine is presented by Listing 2.

```

Listing 2. Code fragment of monitor engine

sequence first( reg[7:0] a, reg[7:0]b);

reg[7:0] d;

(!RST,d=a)

##7 (b==d);

endsequence

property f(a,b);

@(posedge CLK)

// disable iff(RST]|$isunknown(a)) first(a,b);

!RST |=> first(a,b);

endproperty

odin:assert property (f(xin,xa7_in))

// $display("Very good");

else $error("The end, xin =%b,xa7_in=%b", $past(xin,

7),xa7_in);

```

Testing of discrete cosine transformation in the environment Riviera, Aldec detects incorrectness in seven rows of HDL-models:

//add\_sub1a <= xa7\_reg + xa0\_reg;//

Subsequent correcting code allowed obtaining the following code (Listing 3).

```

Listing 3. Corrected code fragment

add_sub1a <= ({xa7_reg[8],xa7_reg} +

{xa0 reg[8],xa0 reg});

add_sub2a <= ({xa6_reg[8],xa6_reg}

+{xa1_reg[8],xa1_reg});

add_sub3a <= ({xa5_reg[8],xa5_reg}

+{xa2_reg[8],xa2_reg});

add_sub4a <= ({xa4_reg[8],xa4_reg} +

{xa3_reg[8],xa3_reg});

end

else if (toggleA == 1'b0)

beain

add_sub1a <= ({xa7_reg[8],xa7_reg} -

{xa0_reg[8],xa0_reg});

add_sub2a <= ({xa6_reg[8],xa6_reg} -

{xa1_reg[8],xa1_reg});

add_sub3a <= ({xa5_reg[8],xa5_reg} -

{xa2_reg[8],xa2_reg});

add_sub4a <= ({xa4_reg[8],xa4_reg} -

{xa3_reg[8],xa3_reg});

```

## 5. Conclusion

1. Infrastructure and technology for cyberspace analysis are presented. Proposed transactional graph model and method for diagnosis of digital systems-on-chips are focused to considerable reducing the time of fault detection and memory for storing the diagnosis matrix by forming ternary relations in the form of test, monitor, and functional component.

2. An improved process model for definition of functional failures in software or hardware is proposed. It is characterized by using the xor-operation, which makes it possible to improve the diagnosis performance for single and multiple faults (functional failures) on the basis of parallel analysis of the fault table, boundary scan standard IEEE 1500, and vector operations and, or, xor.

3. A model for diagnosing the functionality of digital system-on-chip in the form of multitree and method for tree traversal, implemented in the engine for detecting faults with given depth, are developed. They consider-

ably increase the performance of software and hardware Infrastructure IP.

4. Test verification of proposed diagnosis method is performed by three real case studies, presented by SoC functionalities of a cosine transform filter, which showed the consistency of the results in order to minimize the time of fault detection and memory for storing diagnostic information, as well as increase the diagnosis depth for digital products.

## 6. References

- Technical diagnosis basics / Editor P.P. Parchomenko.-M.: Energy.- 1976.- 460 p.

- [2] Parchomenko P.P., Sogomonyan E.S. Technical diagnosis basics (Optimization of diagnosis algorithms, hardware tools) / Editor P.P. Parchomenko.- M.: Energy.-1981.- 320 p.

- [3] Infrastructure for brain-like computing / M.F. Bondaryenko, O.A. Guz, V.I. Hahanov, Yu.P. Shabanov-Kushnaryenko.– Kharkov: Novoye Slovo.– 2010.– 160 p.

- [4] Design and Verification of digital systems on chips / V.I. Hahanov, I.V. Hahanova, E.I. Litvinova, O.A. Guz.– Kharkov: Novoye Slovo. – 2010. – 528 p.

- [5] Semenets V.V., Hahanova I.V., Hahanov V.I. Design of digital systems by using VHDL language.– Kharkov: KHNURE.– 2003.– 492 p.

- [6] Hahanov V.I., Hahanova I.V. VHDL+Verilog = synthesis for minutes. – Kharkov: KHNURE. – 2006. – 264 p.

- [7] IEEE Standard for Reduced-Pin and Enhanced-Functionality Test Access Port and Boundary-Scan Architecture IEEE Std 1149.7-2009. – 985 p.

- [8] Da Silva F., McLaurin T., Waayers T. The Core Test Wrapper Handbook. Rationale and Application of IEEE Std. 1500<sup>TM</sup>. –Springer.– 2006.– XXIX.– 276 p.

- [9] Marinissen E.J., Yervant Zorian. Guest Editors' Introduction: The Status of IEEE Std 1500.–IEEE Design & Test of Computers.– 2009.– No26(1).– P.6-7.

- [10] Benso A., Di Carlo S., Prinetto P., Zorian Y. IEEE Standard 1500 Compliance Verification for Embedded Cores // IEEE Trans. VLSI Syst.– 2008.– No 16(4).– P. 397-407.

- [11] Hahanov V.I., Litvinova E.I., Chumachenko S.V., Guz O.A. Logic associative computer // Electronic simulation.– No 1.– 2011.– P.73-83.

Camera-ready was prepared in Kharkov National University of Radio Electronics Lenin Ave, 14, KNURE, Kharkov, 61166, Ukraine

> Approved for publication: 26.08.2011. Format 60×841/8. Relative printer's sheets: 42. Circulation: 150 copies. Published by SPD FL Stepanov V.V. Ukraine, 61168, Kharkov, Ak. Pavlova st., 311

Матеріали симпозіуму «Схід-Захід Проектування та Діагностування – 2011» Макет підготовлено у Харківському національному університеті радіоелектроніки Редактори: Володимир Хаханов, Світлана Чумаченко, Євгенія Литвинова Пр. Леніна, 14, ХНУРЕ, Харків, 61166, Україна

> Підписано до публікації: 26.08.2011. Формат 60×84<sup>1</sup>/<sub>8</sub>. Умов. друк. Арк. 42. Тираж: 150 прим. Видано: СПД ФЛ Степанов В.В. Вул. Ак. Павлова, 311, Харків, 61168, Україна