## МИНИСТЕРСТВО ОБРАЗОВАНИЯ И НАУКИ УКРАИНЫ

# ХАРЬКОВСКИЙ НАЦИОНАЛЬНЫЙ УНИВЕРСИТЕТ РАДИОЭЛЕКТРОНИКИ

ISSN 0135-1710

# АВТОМАТИЗИРОВАННЫЕ СИСТЕМЫ УПРАВЛЕНИЯ И ПРИБОРЫ АВТОМАТИКИ

Всеукраинский межведомственный научно-технический сборник

Основан в 1965 г.

Выпуск 145

#### УДК 62-50

В сборнике представлены результаты исследований, касающихся компьютерной инженерии, управления, технической диагностики, автоматизации проектирования, оптимизированного использования компьютерных сетей и создания интеллектуальных экспертных систем. Предложены новые подходы, алгоритмы и их программная реализация в области автоматического управления сложными системами, оригинальные информационные технологии в науке, образовании, медицине.

Для преподавателей университетов, научных работников, специалистов, аспирантов.

У збірнику наведено результати досліджень, що стосуються комп'ютерної інженерії, управління, технічної діагностики, автоматизації проектування, оптимізованого використання комп'ютерних мереж і створення інтелектуальних експертних систем. Запропоновано нові підходи, алгоритми та їх програмна реалізація в області автоматичного управління складними системами, оригінальні інформаційні технології в науці, освіті, медицині.

Для викладачів університетів, науковців, фахівців, аспірантів.

#### Редакиионная коллегия:

B.B. Семенец, д-р техн. наук, проф. (гл. ред.),  $M.\Phi$ . Бондаренко, д-р техн. наук, проф.,  $U.\mathcal{A}$ . Горбенко, д-р техн. наук, проф.,  $E.\Pi$ . Путятин, д-р техн. наук, проф.,  $B.\Pi$ . Тарасенко, д-р техн. наук, проф.,  $\Gamma.M$ . Загарий, д-р техн. наук, проф.,  $\Lambda.$ Штефан, докторинженер,  $\Gamma.\Phi$ . Кривуля, д-р техн. наук, проф.,  $O.\Gamma$ . Руденко, д-р техн. наук, проф., H.B. Алипов, д-р техн. наук, проф., E.B. Бодянский, д-р техн. наук, проф.,  $\mathcal{B}.\mathcal{M}$ . Левыкин, д-р техн. наук, проф.,  $\mathcal{B}.\mathcal{M}$ . Хаханов, д-р техн. наук, проф.,  $\mathcal{B}.\mathcal{M}$ . Хаханов, д-р техн. наук, проф.,  $\mathcal{B}.\mathcal{M}$ . Хаханов, д-р техн. наук, проф. (отв. ред.).

Свидетельство о государственной регистрации печатного средства массовой информации

КВ № 12073-944ПР от 07.12.2006 г.

Адрес редакционной коллегии: Украина, 61166, Харьков, просп. Ленина, 14, Харьковский национальный университет радиоэлектроники, комн. 321, тел. 70-21-326

© Харківський національний університет радіоелектроніки, 2008

# СОДЕРЖАНИЕ

| ЕВЛАНОВ М.В., СЛИПЧЕНКО Е.В., НИКИТЮК В.А.                     |

|----------------------------------------------------------------|

| ПОДХОД К ПРОЕКТИРОВАНИЮ ХРАНИЛИЩ ДАННЫХ ВИНФОРМАЦИОННЫХ        |

| СИСТЕМАХ4                                                      |

| БАБИЧ А.В., КУДИНА М.В., ЕМЕЛЬЯНОВ И.В.                        |

| ИССЛЕДОВАНИЕ МЕТОДОВ РЕШЕНИЯ ЗАДАЧИНЖИНИРИНГА ТРАФИКА ВСЕТЯХ   |

| СЛЕДУЮЩЕГО ПОКОЛЕНИЯ8                                          |

| ЗАЙЧЕНКО С.А., ХАХАНОВ В.И.                                    |

| ФОРМАЛЬНАЯ СЕМАНТИКА СЛОЖНЫХ ОПЕРАТОРОВ ЛИНЕЙНОЙ ТЕМПОРАЛЬНОЙ  |

| ЛОГИКИ14                                                       |

| ОЛІЙНИК О.І.                                                   |

| ЧИСЕЛЬНЕ МОДЕЛЮВАННЯ ДИФУЗІЙНИХ ПРОЦЕСІВ У СИСТЕМАХ З МАСИВАМИ |

| ЗАГЛИБЛЕНИХ МІКРОЕЛЕКТРОДІВ У ФОРМІ ДИСКУ29                    |

| ЛИТВИНОВА Е.И.                                                 |

| ТЕХНОЛОГИИ ВСТРОЕННОГО РЕМОНТА КОМПОНЕНТОВ SYSTEM-IN-PACKAGE40 |

| ТЕВЯШЕВ А.Д., ЗОЛОТАРЕВ Д.А.                                   |

| ОБ ОДНОМ МЕТОДЕ РЕШЕНИЯ ЗАДАЧИ ОПТИМИЗАЦИИ ПЛАНОВЫХ РЕЖИМОВ    |

| ТРАНСПОРТА И РАСПРЕДЕЛЕНИЯ ПРИРОДНОГО ГАЗА ВГОРОДСКИХ          |

| ГАЗОРАСПРЕДЕЛИТЕЛЬНЫХ СЕТЯХ48                                  |

| ЧУБ И.А., НОВОЖИЛОВА М.В.                                      |

| МОДИФИКАЦИЯ ТОЧНОГО МЕТОДА РЕШЕНИЯ ЗАДАЧИ РАЗМЕЩЕНИЯ           |

| ПРЯМОУГОЛЬНЫХ ОБЪЕКТОВ57                                       |

| ТАЯНОВ С.А., ТАЯНОВ В.А.                                       |

| МЕТОДИКА КЛАСТЕРИЗАЦІЇ ЗОБРАЖЕНЬ ДЛЯ ЇХ КОМПРЕСІЇ НА ОСНОВІ    |

| КОМПОНЕНТНОГО АНАЛІЗУ63                                        |

| ШАХОВСЬКА Н.Б., УГРИН Д.І.                                     |

| ТЕХНОЛОГІЯ ЕТЬ В ІНТЕГРАЦІЇ ДАНИХ ТУРИСТИЧНОГО БІЗНЕСУ         |

| ДОЛГОВА Н.Г., НОВОЖИЛОВА М.В., СИНЕЛЬНИКОВА О.И.               |

| МЕТОД ОЦЕНКИ АЛЬТЕРНАТИВНЫХ ВАРИАНТОВ ФУНКЦИОНАЛЬНОГО          |

| ЗОНИРОВАНИЯ ТЕРРИТОРИИ ГОРОДА73                                |

| ЕВГРАФОВ В.Н.                                                  |

| ПРОИЗВОДИТЕЛЬНОСТЬ БУФЕРНЫХ АСИНХРОННЫХ МНОГОСТУПЕНЧАТЫХ СЕТЕЙ |

| С ПРОИЗВОЛЬНЫМ ЧИСЛОМ ПРИОРИТЕТНЫХ МОДУЛЕЙ ПАМЯТИ80            |

| КАКУРИН Н.Я., КОВАЛЕНКО С.Н., ЛОПУХИН Ю.В., МАКАРЕНКО А.Н.     |

| СПОСОБ ПОВЫШЕНИЯ БЫСТРОДЕЙСТВИЯ ПРЕОБРАЗОВАТЕЛЕЙ КОДОВ         |

| НА СЧЕТЧИКАХ86                                                 |

| ЗАЯЦЬ В.М.                                                     |

| ПЕРСПЕКТИВИ ЗАСТОСУВАННЯ АВТОМАТИЗОВАНОЇ СИСТЕМИ РОЗПІЗНАВАННЯ |

| ТА ІДЕНТИФІКАЦІЇ КОРИСТУВАЧІВ КОМП'ЮТЕРА, ОПИСАНОЇ НА ОСНОВІ   |

| ДИСКРЕТНОЇ МОДЕЛІ96                                            |

| ЛЫСЕНКО Э.В., ПОНОМАРЕНКО В.П., ПИСКЛАКОВА В.П.                |

| СИСТЕМОЛОГИЧЕСКИЙ АНАЛИЗ ПРОБЛЕМЫ ПРИНЯТИЯ РЕШЕНИЙ В УСЛОВИЯХ  |

| МНОГОКРИТЕРИАЛЬНОСТИ И НЕОПРЕДЕЛЕННОСТИ104                     |

| ВИШНЯК М.Ю., ДОВГАНЬ С.С.                                      |

| РАСШИРЕНИЕ ФУНКЦИЙ АСУ: УПРАВЛЕНИЕ ЗНАНИЯМИ109                 |

| ОМРИ КАРИМ                                                     |

| ПОСТРОЕНИЕ АЛГОРИТМА РАСПОЗНАВАНИЯ ОТПЕЧАТКОВ ПАЛЬЦЕВ          |

| ДЛЯ СИСТЕМЫ КОНТРОЛЯ ДОСТУПА116                                |

| КРИВУЛЯ Г.Ф., РЯБЕНЬКИЙ В.М., ПЕТРЕНКОЛ.П.                     |

| МЕТОДИКА ФОРМИРОВАНИЯ МАТЕМАТИЧЕСКОЙ МОДЕЛИ СУММАТОРА          |

| В ФОРМАТЕ ТРОИЧНОЙ СИСТЕМЫ СЧИСЛЕНИЯ12                         |

| КУЗЁМИН А. Я., ГОЛОВИЙ (ГУСАРЬ) Н.В., ДАЮБ Я.                  |

| РЕАЛИЗАЦИЯ МОДЕЛИ СИСТЕМЫ ПОДДЕРЖКИ ПРИНЯТИЯ РЕШЕНИЙ В ОБЛАСТИ |

| СЕРВИСНОГО ОБСЛУЖИВАНИЯ БАНКОМАТОВ134                          |

| ВЕРЕЩАК И.А.                                                   |

| МЕТОД НИЗКОУРОВНЕВОЙ ОБРАБОТКИ ГРАФИЧЕСКОЙ ИНФОРМАЦИИ139       |

| DEMEDATIA 143                                                  |

| PRIDRYA 17/1                                                   |

Практическая значимость. Программный комплекс позволяет ускорить разработку MIMD-системы благодаря возможностям расчета ключевых показателей производительности многоступенчатой сети на ранних этапах проектирования. Благодаря предварительной оценке производительности будущей коммутирующей сети, сокращаются затраты на имплементацию пробной версии сети, что уменьшает общую стоимость многопроцессорной системы.

Список литературы: 1. J. Konicek, T. Tilton, et al, The organization of the Cedar system // Prac. Int' Conf. Parallel Processing, Aug. 1991.P. 49-56. 2. Y. Mun and H.Y. Youn. Performance analysis of finite buffered multistage interconnection networks // IEEE Trans. Computers, Feb. 1994. P. 153-162. 3. Prasant Mohapatra, Chita R. Das. Performance Analysis of Finite-Buffered Asynchronous Multistage Interconnection Networks, IEEE Transactions on Parallel and Distributed Systems, Vol. 7, No. 1. 1996. P. 18–25. 4. El-Paoumy, On Truncated Erlangian Queuing Systems with State-Dependent Service Rate, Balking and Reneging, Applied Mathematical Sciences, Vol. 2. 2008. P. 1161-1167. 5. Dickey S.R. and Percus O.E. Performance differences among combining switch architectures, Proc. I&Z, Conf. on Parallel Processing, Aug. 1992. Vol. 1. P. 110-117.

Поступила в редколлегию 15.12.2008

**Евграфов Вячеслав Николаевич**, аспирант кафедры ПМ ХНУРЭ. Научные интересы: многопроцессорные системы, многоступенчатые сети. Адрес: Украина, 61166, Харьков, пр. Ленина, 14, тел. 8(063)95-82-985.

УДК 681.325.53

Н.Я. КАКУРИН, С.Н. КОВАЛЕНКО, Ю.В. ЛОПУХИН, А.Н. МАКАРЕНКО

## СПОСОБ ПОВЫШЕНИЯ БЫСТРОДЕЙСТВИЯ ПРЕОБРАЗОВАТЕЛЕЙ КОДОВ НА СЧЕТЧИКАХ

Предлагается способ повышения быстродействия преобразователей кодов на счетчиках с помощью параллельной стратегии использования шагов преобразования. Разрабатывается метод расчета числа тактов преобразования и программное обеспечение для его реализации.

#### 1. Постановка задачи

Одношаговый преобразователь кодов по методу накопления эквивалентов обладает небольшими аппаратурными затратами, но требует К тактов на преобразование числа [1]. При более высоких требованиях к быстродействию применяют двухшаговые, трехшаговые и другие преобразователи кодов с большим числом различных преобразований шагов [2-5].

Для максимального числа тактов преобразования  $N_i^{др}$  ПК дробных чисел в работах [1,2] была получена система формул

$$\begin{array}{c} N_1^{\pi p} = K-1; \\ N_2^{\pi p} = ](K-1)/a[+a-1; \\ N_3^{\pi p} = ](K-1)/b[+](b-1)/a[+a-1; \\ N_4^{\pi p} = ](K-1)/c[+](c-1)/b[+](b-1)/a[+a-1; \end{array} \eqno(1)$$

где K — основание системы счисления на входе; a,b,c — соответственно второй, третий и четвертый шаги преобразования (первый шаг преобразования равен 1);  $N_1^{,ap}$ ,  $N_2^{,ap}$ ,  $N_3^{,ap}$ ,  $N_4^{,ap}$  — максимальное число тактов преобразования соответственно одношагового, двухшагового, трехшагового и четырехшагового ПК.

В процессе преобразования применяется стратегия последовательного использования шагов преобразования, т.е. показание разрядных счетчиков вначале уменьшается на величину наибольшего шага. Затем, если во всех разрядах значения цифр оказываются меньше величины наибольшего шага, происходит переход на меньший шаг; затем на последнем этапе преобразования происходит переход на первый шаг, равный 1, и преобразование выполняется до полного обнуления всех разрядных счетчиков.

Увеличение числа различных шагов преобразования целесообразно, если уменьшается максимальное число тактов преобразования. Из всех возможных значений шагов преобра-

зования целесообразно выбирать их по возможности большими и равными степени двойки. В этом случае аппаратурные затраты на построение других узлов ПК, таких как кодовые шифраторы (субтракторы) и дешифраторы нуля, а также дешифраторы превышения будут иметь меньшее значение. Эффект увеличения быстродействия для K=3-12 в двухшаговом ПК значителен и по сравнению с одношаговым составляет 1,33-1,71. При более высоких требованиях быстродействия следует использовать трехшаговый ПК.

### 2. Структура и функционирование трехшагового ПК

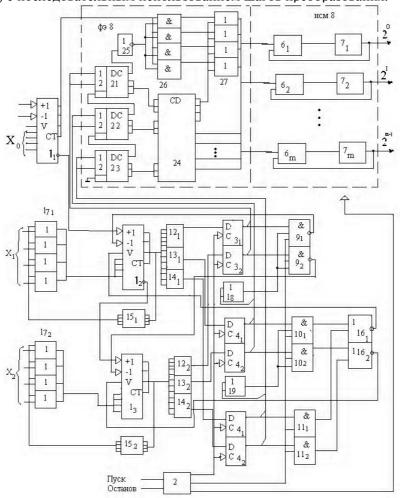

Рассмотрим структуру и функционирование трехшагового преобразователя кодов целых чисел (рис.1) с последовательным использованием шагов преобразования.

Рис. 1. Структура трехшагового ПК

ПК содержит группу разрядных счетчиков I, генератор импульсов 2 (блок управления), содержащий прямой П, прямые задержанные ПЗ1 и ПЗ2 И выходы, первую группу триггеров 3 состояния, вторую группу триггеров 4 состояния, третью группу триггеров 5 состояния, комбинационный двоичный сумматор 6 и регистр 7 результата, образующие в совокупности накапливающий сумматор 8, первую группу элементов И-НЕ 9, вторую и третью группы элементов И 10, И 11, группу дешифраторов нуля 12, первую группу дешифраторов превышения 13, вторую группу дешифраторов превышения 14, группу шифраторов 15, первую группу элементов ИЛИ-НЕ 16, (*n-1*) - группу элементов ИЛИ 17, первый элемент ИЛИ-НЕ 18, второй элемент ИЛИ-НЕ 19, формирователь эквивалента 20, включающий в свой состав первый 21, второй 22, третий 23 дешифраторы и шифратор 24.

В состав формирователя эквивалентов (ФЭ) 20 также входит инвертор НЕ 25, группа элементов И 26, группа элементов ИЛИ 27. Первая группа триггеров 3 фиксирует ненулевое значение счетчиков соответствующих разрядов. Вторая группа триггеров состояния 4

фиксирует значение счетчиков соответствующих разрядов, превышающее заданное число и, например 1. Третья группа триггеров состояния 5 фиксирует значение счетчиков соответствующих разрядов, превышающее заданное число a, например 3. Шифраторы 15 реализуют функцию:

$$y = x - a; a \le x < b;$$

$$y = x - a; a \le x < b;$$

$$x; x < a,$$

(2)

где x – входной код; a – параметр (второй шаг преобразования), в частном случае, равный 2; b – параметр (третий шаг преобразования), в частном случае, равный 4.

Цепи инициирования и сброса на рис. 1 не показаны. Так как в конкретном случае n=3; K=12, то диапазон изменения входного кода  $0-(12^3-1)$ . Код состояния триггеров как первой группы 3, так и второй группы 4, а также третьей группы 5 имеет  $2^2=4$  значения от 00 до 11. В данном ПК двоично-К-ичного кода в двоичный код  $\Phi$ 9 20, выполненный в виде последовательного соединения первого 21, второго 22 и третьего 23 дешифраторов,

$$KC_{1} + K^{2}C_{2}; E_{1} = E_{2} = D_{1} = D_{2} = 0;$$

$$S = AKD_{1} + AK^{2}D_{2}; E_{1} = E_{2} = 0 \text{ m } D_{1}, D_{2} \neq 0;$$

$$bKE_{1} + bK^{2}E_{2}; E_{1}, E_{2} \neq 0;$$

(3)

где  $C_1C_2$  — значения разрядов двоичного кода триггеров состояний первой группы 3;  $D_1D_2$  — значения разрядов двоичного кода триггеров состояния второй группы 4;  $E_1E_2$  — значения разрядов двоичного кода триггеров состояния третьей группы 5.

Каждый из  $C_m$  (m=1,2) разрядов кода триггеров 3 первой группы состояний разрядных счетчиков соответствует наличию (1) или отсутствию (0) информации в соответствующем старшем разряде преобразуемого кода, а разряд  $D_m$  (m=1,2) триггеров 4 второй группы состояний разрядных счетчиков равен 1, если соответствующий разряд преобразуемого кода имеет значение  $x_i \geq a(1 < a < b)$ , в противном случае  $D_m = 0$ ; разряд  $E_m$  (m=1,2) триггеров 5 третьей группы состояния разрядных счетчиков равен 1, если соответствующий разряд преобразуемого кода имеет значение  $x_i \geq b(a < b \leq K-1)$ , в противном случае  $E_m = 0$ . ФЭ 20 преобразует вначале двоичный код  $E_1, E_2$  триггеров состояния третьей группы, затем при  $E_1 = E_2 = 0$  и  $D_1$ ,  $D_2 \neq 0$  — двоичный код  $D_1, D_2$  триггеров состояния второй группы, затем при  $E_1 = E_2 = D_1 = D_2 = 0$  и  $C_1$ ,  $C_2 \neq 0$  — двоичный код  $C_1$ ,  $C_2$  триггеров состояний первой группы и при  $E_1 = E_2 = D_1 = D_2 = C_1 = C_2 = 00$  выполняет трансляцию (передачу) двоично-К-ичного кода младшего разряда в двоичный код эквивалента на выходе.

Преобразование числа выполняется по принципу последовательного использования шагов; вначале третий шаг b; затем второй шаг a, наконец, шаг 1. При поступлении импульсов генератора 2 с выхода П информация о состоянии разрядных счетчиков заносится в регистры состояний,  $\Phi$ Э выдает код эквивалента, соответствующий состояниям регистров 3,4,5; затем из состояний разрядных счетчиков 1 вычитается значение текущего шага (по заднему фронту 0-1 импульса с выхода 11,31. И, наконец, по заднему фронту 1-0 импульса с выхода ПЗ2 выполняется прибавление эквивалента в накапливающий сумматор 8. Описанная последовательность действий повторяется циклически до обнуления всех старших разрядных счетчиков.

Рассмотрим пример преобразования числа 7926<sub>10</sub> из двоично-десятичной системы в двоичную в трехшаговом ПК последовательного типа с набором шагов 1,2,4 (табл. 1.).

реализует функцию:

Таблица 1

| ый                  | та          | Состояние разрядных<br>счетчиков |                    | Коды с            | остоянийтр            | на<br>нта         | Значение<br>сумматора   |                 |             |

|---------------------|-------------|----------------------------------|--------------------|-------------------|-----------------------|-------------------|-------------------------|-----------------|-------------|

| Используемый<br>шаг | Номер такта | Начало<br>такта                  | Коне<br>ц<br>такта | Третий<br>регистр | Второй<br>регист<br>р | Первый<br>регистр | Величина<br>эквивалента | Начало<br>такта | Конец такта |

| A                   | N           | $x_4x_3x_2x_1$                   | $x_4 x_3 x_2 x_1$  | $E_3E_2E_1$       | $D_3D_2D_1$           | $C_3C_2C_1$       | ΕФ                      | CM              | CM          |

|                     | 0           | 7926                             | 7926               | 000               | 000                   | 000               | 0000                    | 0000            | 0000        |

| 4                   | 1           | 7926                             | 3526               | 110               | 111                   | 111               | 4400                    | 0000            | 4400        |

| 4                   | 2           | 3526                             | 3126               | 010               | 111                   | 111               | 400                     | 4400            | 4800        |

| 2                   | 3           | 3126                             | 1106               | 000               | 101                   | 111               | 2020                    | 4800            | 6820        |

| 1                   | 4           | 1106                             | 0006               | 000               | 000                   | 110               | 1100                    | 6820            | 7920        |

|                     | 5           | 0006                             | 0006               | 000               | 000                   | 000               | 6                       | 7920            | 7926        |

# 3. Проектирование формирователей эквивалентов для трехшаговых преобразователей последовательного типа

Методику проектирования  $\Phi$ Э рассмотрим на примере трехразрядного трехшагового ПК (табл. 2).

Таблица 2

| 4       | Коды состоя | ний триггер | ов групп |                       | Десятич-               | ч-                                        |      |                                                             |  |

|---------|-------------|-------------|----------|-----------------------|------------------------|-------------------------------------------|------|-------------------------------------------------------------|--|

| Номер   | Третьей     | Второй      | Первой   | Общий вид эквивалента | ный<br>эквива-<br>лент | Двоичный кодэквивален                     |      | ивалента                                                    |  |

| $Z_{i}$ | $E_2E_1$    | $D_2D_1$    | $C_2C_1$ | S                     | S <sub>10</sub>        | $y_{10}y_9$ $y_8y_7y_6y_5$ $y_4y_3y_2y_5$ |      | y <sub>4</sub> y <sub>3</sub> y <sub>2</sub> y <sub>1</sub> |  |

| 0       | 00          | 00          | 00       | x <sub>0</sub>        | $\mathbf{x}_0$         | Трансляция тетрады x 0                    |      |                                                             |  |

| 1       | 00          | 00          | 01       | K                     | 12                     | 00                                        | 0000 | 1100                                                        |  |

| 2       | 00          | 00          | 10       | $K^2$                 | 144                    | 00                                        | 1001 | 0000                                                        |  |

| 3       | 00          | 00          | 11       | $K^2 + K$             | 156                    | 00                                        | 1001 | 1100                                                        |  |

| 4       | 00          | 01          | X1       | aK                    | 24                     | 00                                        | 0001 | 1000                                                        |  |

| 5       | 00          | 10          | 1X       | aK <sup>2</sup>       | 288                    | 01                                        | 0010 | 0000                                                        |  |

| 6       | 00          | 11          | 11       | $aK^2 + aK$           | 312                    | 01                                        | 0011 | 1000                                                        |  |

| 7       | 01          | X1          | X1       | bK                    | 48                     | 00                                        | 0011 | 0000                                                        |  |

| 8       | 10          | 1X          | 1X       | bK <sup>2</sup>       | 576                    | 10                                        | 0100 | 0000                                                        |  |

| 9       | 11          | 11          | 11       | $bK^2 + bK$           | 624                    | 10                                        | 0111 | 0000                                                        |  |

Шифраторы 15 формируют выходное слово, меньшее на 4 единицы по отношению к входному слову при  $x_i \ge 4$  (если a = 4), меньшее на 2 единицы по отношению к входному слову при  $2 \le x_i < 4$  (если a = 2) и равное входному слову при  $x_i < 2$ .

$\Phi$ Э 20 при n=3 и K=12 реализует функцию:

Преобразование двоичных кодов триггеров состояний первой 3, второй 4 и третьей 5 групп соответствует табл. 2.

ФЭ для ПК последовательного типа реализуем на основе трех последовательно включенных ДШ 21-23, выходы группы из четырех элементов И 26 поступают на соответствующие входы четырех элементов ИЛИ 27, вторые входы которых соединены с выходами четырех младших разрядов шифратора 24 (рис. 1).

Функции выходов шифратора 24 в целях сокращения аппаратных затрат реализуют с учетом общих частей по следующим выражениям:

$$\begin{aligned} y_1 &= y_2 = 0; \ y_7 = y_{10} = E_2 \ ; \ y_9 = \overline{Z_5} \left| \overline{Z_6} = M_1, \ M_2 = \overline{Z_4} \right| \overline{Z_6}; \ M_3 = \overline{Z_7} \left| \overline{Z_9}; \ M_4 = y_8 = \overline{Z_2} \right| \overline{Z_3} \ , \\ M_5 &= y_3 = \overline{Z_1} \left| \overline{Z_3}; \ y_4 = M_2 \cup M_5; \ \ y_5 = M_2 \cup M_3 \cup M_4 \ ; \ y_6 = M_1 \cup M_3. \end{aligned} \tag{5}$$

В целях минимизации числа корпусов ЛЭ для реализации разрядных функций  $\Phi$ Э можно использовать ПЛМ типа K556PT1, с параметрами s, t, q(16,8,48).

И на четвертом этапе будет затрачен еще один такт на трансляцию младшей цифры.

Следовательно,  $N_3 = \frac{1}{b-1} / \frac{b-1}{a} = \frac{1}{a-1} + \frac{1}{a-1} = \frac{1}{b-1} / \frac{b-1}{a} = \frac{1}{a-1} + \frac{1}{a-1} = \frac{1}{a$

## 4. Повышение быстродействия ПК параллельного типа

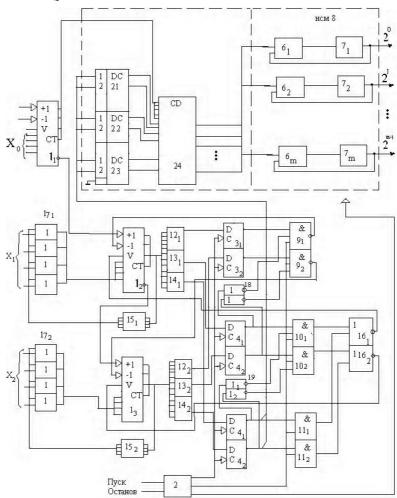

Структура трехшагового ПК параллельного типа содержит вентили опроса, каждый из которых управляется через инвертор от триггера соответствующего разряда старшего регистра состояний (рис. 2).

Рис. 2. Структура трехшагового ПК с параллельным использованием шагов преобразования Для трехшагового ПК параллельного типа вначале составляют таблицу закона функционирования  $\Phi \ni (\text{табл.3})$ .

| 7               | Коды состоя | яний триггер                  | ов групп |                       | Десятич         |                                |          |                                                             |  |

|-----------------|-------------|-------------------------------|----------|-----------------------|-----------------|--------------------------------|----------|-------------------------------------------------------------|--|

| Номер<br>строки | Третьей     | Второй                        | Первой   | Общий вид эквивалента | ный<br>эквивале | Двоичный код эквивалента       |          |                                                             |  |

| H 15            | третвен     | Бторой                        | Первои   | экынышенти            | НТ              |                                |          |                                                             |  |

| $Z_{i}$         | $E_2E_1$    | Д <sub>2</sub> Д <sub>1</sub> | $C_2C_1$ | S                     | S <sub>10</sub> | y <sub>10</sub> y <sub>9</sub> | У8У7У6У5 | y <sub>4</sub> y <sub>3</sub> y <sub>2</sub> y <sub>1</sub> |  |

| 0               | 00          | 00                            | 00       | $\mathbf{x}_0$        | $\mathbf{x}_0$  | Трансляция тетрады $x_0$       |          |                                                             |  |

| 1               | 00          | 00                            | 01       | K                     | 12              | 2 00 0000 11                   |          | 1100                                                        |  |

| 2               | 00          | 00                            | 10       | K <sup>2</sup>        | 144             | 00                             | 1001     | 0000                                                        |  |

| 3               | 00          | 00                            | 11       | K <sup>2</sup> + K    | 156             | 00                             | 1001     | 1100                                                        |  |

| 4               | 00          | 01                            | 01       | aK                    | 24              | 00                             | 0001     | 1000                                                        |  |

| 5               | 00          | 10                            | 11       | $K^2 + aK$            | 168             | 00                             | 1010     | 1000                                                        |  |

| 6               | 00          | 10                            | 10       | aK <sup>2</sup>       | 288             | 01                             | 0010     | 0000                                                        |  |

| 7               | 00          | 10                            | 11       | $aK^2 + K$            | 300             | 01                             | 0010     | 1100                                                        |  |

| 8               | 00          | 11                            | 11       | $aK^2 + aK$           | 312             | 01                             | 0011     | 1000                                                        |  |

| 9               | 01          | 01                            | 01       | bK                    | 48              | 00                             | 0011     | 0000                                                        |  |

| 10              | 01          | 01                            | 11       | $K^2 + bK$            | 192             | 00                             | 1100     | 0000                                                        |  |

| 11              | 01          | 11                            | 11       | $aK^2 + bK$           | 336             | 01                             | 0101     | 0000                                                        |  |

| 12              | 10          | 10                            | 10       | bK <sup>2</sup>       | 576             | 10                             | 0100     | 0000                                                        |  |

| 13              | 10          | 10                            | 11       | bK <sup>2</sup> +K    | 588             | 10                             | 0100     | 1100                                                        |  |

| 14              | 10          | 11                            | 11       | bK <sup>2</sup> +aK   | 600             | 10                             | 0101     | 1000                                                        |  |

| 15              | 11          | 11                            | 11       | $bK^2 + bK$           | 624             | 10                             | 0111     | 0000                                                        |  |

Затем находят запись разрядных функций шифратора:

$$y_{1} = y_{2} = 0; y_{9} = \overline{Z_{6}} | \overline{Z_{7}} | \overline{Z_{8}} | \overline{Z_{11}}; y_{10} = E_{2}; y_{8} = \overline{Z_{5}} | \overline{Z_{10}};$$

$$y_{7} = \overline{Z_{10}} | \overline{Z_{11}} | \overline{Z_{12}} | \overline{Z_{13}} | \overline{Z_{14}} | \overline{Z_{15}}; y_{6} = \overline{Z_{5}} | \overline{Z_{6}} | \overline{Z_{7}} | \overline{Z_{8}} | \overline{Z_{9}} | \overline{Z_{15}};$$

$$y_{5} = \overline{Z_{2}} | \overline{Z_{3}} | \overline{Z_{4}} | \overline{Z_{8}} | \overline{Z_{9}} | \overline{Z_{11}} | \overline{Z_{14}} | \overline{Z_{15}};$$

$$y_{4} = \overline{Z_{1}} | \overline{Z_{3}} | \overline{Z_{4}} | \overline{Z_{5}} | \overline{Z_{7}} | \overline{Z_{8}} | \overline{Z_{13}} | \overline{Z_{14}}; y_{3} = \overline{Z_{1}} | \overline{Z_{3}} | \overline{Z_{7}} | \overline{Z_{13}};$$

$$(6)$$

ФЭ для трехшагового ПК с параллельным использованием шагов реализует функции:

$$Y4 = \overline{z}_{1}/\overline{z}_{3}/\overline{z}_{4}/\overline{z}_{5}/\overline{z}_{7}/\overline{z}_{8}/\overline{z}_{13}/\overline{z}_{14}; Y10 = \overline{z}_{12}/\overline{z}_{13}/\overline{z}_{14}/\overline{z}_{15}; Y5 = \overline{z}_{2}/\overline{z}_{3}/\overline{z}_{4}/\overline{z}_{8}/\overline{z}_{9}/\overline{z}_{11}/\overline{z}_{14}/\overline{z}_{15}; Y6 = \overline{z}_{5}/\overline{z}_{6}/\overline{z}_{7}/\overline{z}_{8}/\overline{z}_{9}/\overline{z}_{15}; Y1 = 0; Y2 = 0; Y3 = \overline{z}_{7}/\overline{z}_{13}; Y7 = \overline{z}_{10}/\overline{z}_{11}/\overline{z}_{12}/\overline{z}_{13}/\overline{z}_{14}/\overline{z}_{15}; Y8 = \overline{z}_{2}/\overline{z}_{3}/\overline{z}_{5}/\overline{z}_{10}; Y9 = \overline{z}_{6}/\overline{z}_{7}/\overline{z}_{8}/\overline{z}_{11}.$$

(7)

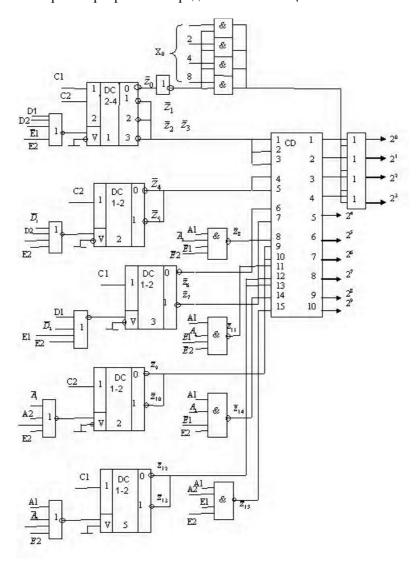

Сравнение табл. 3 и табл. 2 показывает, что количество строк в табл.3 равно 16, а в табл.2 — 10. Особенностью ФЭ для ПК параллельного типа является отказ от принципа последовательного соединения стробируемых дешифраторов (в схеме без параллельного использования шагов) и применение ряда вентилей (схем И), позволяющих выделить определенное подмножество входных наборов (рис.3). Как следует из рис. 3, в схеме ФЭ используется один ДШ 2-4 и четыре ДШ 1-2, девять схем И-НЕ и ИЛИ-НЕ. Таким образом, количество аппаратурных затрат при параллельном использовании шагов преобразования небольшое (15-20% при увеличении быстродействия на 66,7%)

### 5. Метод расчета числа тактов преобразования для различных стратегий

Для расчета числа тактов преобразований ПК, как с последовательной, так и с параллельной стратегиями использования шагов преобразования можно применить методмоделирования преобразования с помощью таблиц (табл.4; табл.5), характеризующих состояние разрядных счетчиков в соответствующий такт.

Таблица 4

| Такт | Набор шагов1,7,8 |

|------|------------------|

| 0    | 98765 43210      |

| 1    | 10054 32100      |

| 2    | 00043 21000      |

| 3    | 00032 10000      |

| 4    | 00001 00000      |

| 5    | 00010 00000      |

| 6    | 00000 00000      |

Таблица 5

| Такт | Набор шагов 1,2,6 |

|------|-------------------|

| 0    | 98765 43210       |

| 1    | 32103 21000       |

| 2    | 10001 00000       |

| 3    | 00000 00000       |

В табл.4 и 5 приведены примеры преобразований для параллельной стратегии использования шагов преобразования. Из табл.5 следует, что набор шагов 1,2,6 позволяет в два раза увеличить быстродействие (три такта преобразования вместо шести для набора шагов 1,7,8). Для моделирования всех возможных случаев преобразования исходное число разрядов принимаем равным К (в каждом из разрядов значение цифры равно К-1, К-2,...,1,0). Для определения максимального числа тактов преобразования трехшагового ПК с последовательным использованием шагов преобразования следует применять формулы (1) или разработанное авторами программное средство МАТРИЦА.

Рис. 3. Структура формирователя эквивалента ПК параллельного типа

Для нахождения оптимального значения шагов b и а, при котором число тактов преобразования  $N^{'}_{3}$ , трехшагового ПК минимально используем программу МАТРИЦА (для ПК с последовательным использованием шагов). Задав исходное значение основание К, получим матрицу всевозможных значений  $N^{'}_{3}$ . Для K=10 получим матрицу:

Программа МАТРИЦА рассчитывает максимальное число тактов преобразования, но для конкретно заданного исходного числа конкретный результат можно получить только путем моделирования методом таблиц. Сравнительные результаты числа тактов преобразования последовательной и параллельной стратегии приведены в табл.6.

Таблица 6

| i  | 1,a,b | $N_3$ | N'. | i  | 1,a,b | $N_3$ | $N_3$ |

|----|-------|-------|-----|----|-------|-------|-------|

| 1  | 1,2,3 | 3     | 5   | 15 | 1,4,6 | 4     | 5     |

| 2  | 1,2,4 | 4     | 5   | 16 | 1,4,7 | 3     | 5     |

| 3  | 1,2,5 | 3     | 4   | 17 | 1,4,8 | 4     | 5     |

| 4  | 1,2,6 | 3     | 4   | 18 | 1,4,9 | 4     | 6     |

| 5  | 1,2,7 | 3     | 4   | 19 | 1,5,6 | 4     | 6     |

| 6  | 1,2,8 | 4     | 5   | 20 | 1,5,7 | 4     | 6     |

| 7  | 1,2,9 | 4     | 6   | 21 | 1,5,8 | 4     | 6     |

| 8  | 1,3,4 | 3     | 4   | 22 | 1,5,9 | 4     | 6     |

| 9  | 1,3,5 | 3     | 4   | 23 | 1,6,7 | 5     | 7     |

| 10 | 1,3,6 | 3     | 4   | 24 | 1,6,8 | 5     | 7     |

| 11 | 1,3,7 | 3     | 5   | 25 | 1,6,9 | 5     | 7     |

| 12 | 1,3,8 | 3     | 5   | 26 | 1,7,8 | 6     | 8     |

| 13 | 1,3,9 | 4     | 5   | 27 | 1,7,9 | 6     | 8     |

| 14 | 1,4,5 | 4     | 5   | 28 | 1,8,9 | 7     | 9     |

#### 6. Математические модели, описывающие ФЭ в ПК параллельного типа

Функционирование трехшагового многоблочного формирователя эквивалентов ( $\Phi$ 3) с параллельной стратегией использования шагов преобразования описывается выражением:

$$S_{m} = \sum_{i=(m-1)P+1}^{i=mP} \gamma_{i}(h) K^{i-1} \cdot R_{i}(h), (i = 1, \overline{mP}),$$

(9)

где m – номер блока  $(m=\overline{1,M})$  ; i – номер разряда в блоке m; P – число разрядов в  $\overline{\phantom{a}}$  блоке

$$(P = \frac{n}{M})$$

;  $n$  – число входных преобразуемых разрядов;  $h$  – текущий шаг преобразований;  $M$

— число блоков в разбиении (M =  $\stackrel{n}{\_}$ ) ;  $C_i$  — состояние i-го триггера регистра состояний.

Коэффициент  $\gamma_i$  (h) при степени оснований  $K^{i-1}$  может принимать три значения в зависимости от значений  $D_i$  и  $C_i$  триггеров i-го разряда соответственно старшего и младшего регистров состояний на этапе (такте) преобразования h:

$$\gamma^{i}(h) = \begin{cases} a, D_{i} \neq 0; C_{i} \neq 0; \\ A, D_{i} \neq 0; C_{i} \neq 0; \\ A, D_{i} = 0; C_{i} \neq 0; \\ A, D_{i} = 0; C_{i} \neq 0; \end{cases}$$

$$(10)$$

$$(10)$$

Коэффициент  $R_i(h)$  учитывает вхождение компоненты i-го разряда (ее вклад) в выражение для  $S_m$  блока m и равен:

$$R_{i}(h) = \begin{cases} 0, E_{i} = D_{i} = C_{i} = 0; \\ \sqrt{1}, E_{i} \vee D_{i} \vee C_{i} = 1. \end{cases}$$

(11)

В зависимости от номера текущего такта преобразования h(h=0,H) значения коэффициентов  $\gamma_i(h)$  и  $R_i(h)$  могут изменяться, т.е. являются динамически изменяющимися, что относится также и к величине  $S_m$ .

Процесс преобразования заканчивается, если на каком-либо из тактов преобразования  $D_i$  и  $C_i$  всех блоков оказываются равными нулю. В случае разбиения шестиразрядного ПК и  $\Phi$ Э на 6 блоков имеем следующие выражения для  $S_1$ -  $S_6$ :

$$S_{1} = \gamma_{1}(h)K^{0}R_{1}(h); S_{2} = \gamma_{2}(h)K^{1}R_{2}(h); S_{3} = \gamma_{3}(h)K^{2}R_{3}(h);$$

$$S_{4} = \gamma_{4}(h)K^{3}R_{4}(h); S_{5} = \gamma_{5}(h)K^{4}R_{5}(h); S_{6} = \gamma_{6}(h)K^{5}R_{6}(h).$$

(12)

Число блоков разбиения (декомпозиции) М  $\Phi$ Э и ПК на блоке является делителем числа входных разрядов n. В этом случае все блоки содержат одинаковое число разрядов. Так, при n=6 делителями являются числа 6,3,2,1 (M=1,2,3,6).

При M=3 получим следующие выражения для  $S_m$ :

$$S_{1} = \sum_{i=1}^{i=2} \gamma_{i}(h) K^{i-1} R_{i}(h) = \gamma_{2}(h) K^{1} R_{2}(h) + \gamma_{1}(h) K^{0} R_{1}(h),$$

$$S_{2} = \sum_{i=3}^{i=4} \gamma_{i}(h) K^{i-1} R_{i}(h) = \gamma_{4}(h) K^{3} R_{4}(h) + \gamma_{3}(h) K^{2} R_{3}(h),$$

$$S_{3} = \sum_{i=5}^{i=6} \gamma_{i}(h) K^{i-1} R_{i}(h) = \gamma_{6}(h) K^{5} R_{6}(h) + \gamma_{5}(h) K^{4} R_{5}(h).$$

(13)

При M=2 выражения для вычисления значений  $S_m$  ФЭ преобразуются к виду:

$$S_{1} = \sum_{i=1}^{i=3} \gamma_{i}(h) K^{i-1} R_{i}(h) = \gamma_{3}(h) K^{2} R_{3}(h) + \gamma_{2}(h) K^{1} R_{2}(h) + \gamma_{1}(h) K^{0} R_{1}(h),$$

$$S_{2} = \sum_{i=6}^{i=6} \gamma_{i}(h) K^{i-1} R_{i}(h) = \gamma_{6}(h) K^{5} R_{6}(h) + \gamma_{4}(h) K^{3} R_{4}(h) + \gamma_{3}(h) K^{2} R_{3}(h).$$

(14)

Наконец, при М=1 получим выражение:

$$S_{1} = \sum_{i=1}^{i=6} \gamma_{i}(h)K^{i-1}R_{i}(h) = \gamma_{6}(h)K^{5}R_{6}(h) + \gamma_{4}(h)K^{3}R_{4}(h) + \gamma_{3}(h)K^{2}R_{3}(h) +$$

$$+\gamma_{3}(h)K^{2}R_{3}(h)+\gamma_{2}(h)K^{1}R_{2}(h)+\gamma_{1}(h)K^{0}R_{1}(h).$$

(15)

Следует отметить, что если М является делителем числа n, то все блоки разбиения будут идентичными и иметь одинаковое число разрядов в блоке. Если это условие не выполняется, то последний блок разбиения будет иметь меньшее число разрядов по сравнению с предыдущими.

Так, при n=8 и M=3 будет два блока по три разряда ( $S_1$  и  $S_2$ ) и один блок (третий) с двумя разрядами. Функционирование  $\Phi$ Э этих блоков описывается следующими формулами:

$$\begin{split} S_1 &= \sum_{i=1}^{i=3} \gamma_i(h) K^{i-1} R_i(h) = \gamma_3(h) K^2 R_3(h) + \gamma_2(h) K^1 R_2(h) + \gamma_1(h) K^0 R_1(h), \\ S_2 &= \sum_{i=4}^{i=6} \gamma_i(h) K^{i-1} R_i(h) = \gamma_6(h) K^5 R_6(h) + \gamma_5(h) K^4 R_5(h) + \gamma_4(h) K^3 R_4(h), \\ S_3 &= \sum_{i=7}^{i=8} \gamma_i(h) K^{i-1} R_i(h) = \gamma_8(h) K^7 R_8(h) + \gamma_7(h) K^6 R_7(h). \end{split}$$

#### Выводы

Научная новизна выполненного исследования заключается в следующем:

- 1. Предложен способ повышения быстродействия трехшаговых преобразователей кодов на базе счетчиков, функционирующих по методу накопления эквивалентов и использующих параллельную стратегию шагов преобразования.

- 2. Проведена сравнительная оценка последовательной и параллельной стратегии использования шагов преобразования и разработана методика расчета максимального числа тактов преобразования для обеих стратегий.

*Практическая значимость* исследования состоит в возможности построения более быстродействующих ПК в методике расчета быстродействия и программном обеспечении для его реализации.

Список литературы: 1. А.С. 1126946 5G06F 5/02. Преобразователь двоично-К-ичного кода в двоичный код/А.Н. Слобожанин //Открытия, изобретения. 1984. №44.С.250. 2.А.С. 1647908 5HO3M 7/12. Преобразователь двоично-К-ичного кода в двоичный код/Н.Я.Какурин, Ю.К. Кирьяков, А.Н. Макаренко // Там же. 1991. №17. С. 262-263. 3. А.С. 1783618 5G06F 5/02. Преобразователь двоично-К-ичного кода в двоичный код/ Н.Я.Какурин, А.Н. Макаренко, Д.Ю. Исхаков, В.А. Толмацкий //Открытия, изобретения. 1984. №44. С.250. 4. Патент України 58165 Н03М 7/12 Перетворювач коду Фібоноччі в двійковий код/ М.Я.Какурін, І.В.Купрейчик, Г.М. Макаренко //Промислова власність. 2003. №7. С.4.149 5. Какурин Н.Я., Макаренко А.Н., Старчевский Д.Л. Проектирование алгоритмов функционирования преобразователей двоично-десятичных кодов последовательного типа. Часть 1. Проектирование алгоритмов преобразования // АСУ и приборы автоматики. 2004. Вып.128. С.76-87.

Поступила в редколлегию 14.12.2008

**Какурин Николай Яковлевич**, канд. техн. наук, профессор кафедры автоматизации проектирования вычислительной техники ХНУРЭ. Научные интересы: прикладная теория цифровых автоматов, автоматизация проектирования цифровых устройств. Адрес: Украина, 61166, Харьков, пр.Ленина, 14, тел. 70-21-326.

**Коваленко Сергей Николаевич,** соискатель кафедры АПВТ ХНУРЭ. Научные интересы: цифровые датчики, устройства преобразования кодов, автоматизация проектирования цифровых устройств. Адрес: Украина, 61166, Харьков, пр.Ленина, 14, тел. 70-21-326.

**Лопухин Юрий Владимирович**, ст. преподаватель кафедры АПВТ ХНУРЭ. Научные интересы: проектирование программного обеспечения, автоматизации проектирования цифровых устройств. Адрес: Украина, 61166, Харьков, пр. Ленина, 14, тел. 70-21-326.

**Макаренко Анна Николаевна**, канд. техн. наук, доцент кафедры высшей математики и информационных технологий Харьковского банковского института. Научные интересы: дискретная математика, анализ и синтез преобразователей код-код. Адрес: Украина, 61074, Харьков, пр.Победы, 65, тел. 33-80-564.

#### УДК 681.325.53

**Спосіб підвищення швидкодії перетворювачів кодів на лічильниках** / М.Я. Какурін, С.М. Коваленко, Ю.В. Лопухін, Г.М.Макаренко // АСУ та прилади автоматики. 2008. Вип. 145. С.86-95.

Запропоновано спосіб підвищення швидкодії перетворювачів кодів на базі лічильників, що використовують метод накопичення еквівалентів, за рахунок паралельного використання кроків перетворення. Розглянуто структуру та функціонування швидкодіючого трьохкрокового перетворювача кодів та метод обчислення максимальної кількості кроків перетворення.

Табл. 6. Іл. 3. Бібліогр.: 5 назв.

#### UDC 681.325.53

The way for rising of the speed of code convertors based on a counters/N. Ya Kakyrin, S.N.Kovalenko, Yu. V. Lopukhin, A.N.Makarenko// Management Information System and Devises. 2008. N 145. P.86-95.

The way for rising of the speed of code convertor based on a counters is offered by the parallel using of a conversions steps/ The structure and functioning of the three-steps code convertor and the method for calculation of the maximal quantity of conversions steps are considered.

Tab. 6. Fig. 3 Ref.: 5 items.