KHARKOV NATIONAL UNIVERSITY OF RADIOELECTRONICS

# Proceedings of IEEE East-West Design & Test Symposium (EWDTS'09)

Copyright © 2009 by The Institute of Electrical and Electronics Engineers, Inc.

SPONSORED BY

IEEE Computer Society Test Technology Technical Council

11tc

Moscow, Russia, September 18 – 21, 2009

#### IEEE EAST-WEST DESIGN AND TEST SYMPOSIUM 2009 ORGANISING COMMITTEE

#### **General Chairs**

V. Hahanov – Ukraine Y. Zorian – USA

#### **General Vice-Chairs**

D. Bikov - Russia R. Ubar – Estonia

#### **Program Chairs**

S. Shoukourian – Armenia D. Speranskiy – Russia

#### **Program Vice-Chairs**

M. Renovell – France Z. Navabi – Iran

#### **Steering Committee**

M. Bondarenko – Ukraine V. Hahanov – Ukraine R. Ubar – Estonia Y. Zorian – USA

#### **Publicity Chairs**

R.Ubar - Estonia S. Mosin – Russia

Program Committee E. Evdokimov – Ukraine A. Chaterjee – USA E. Gramatova – Slovakia S. Hellebrand – Germany A. Ivanov – Canada M. Karavay – Russia V. Kharchenko – Ukraine K. Kuchukjan – Armenia A. Matrosova – Russia V. Melikyan - Armenia

- O. Novak Czech Republic

- A. Orailoglu USA

- Z. Peng Sweden

- A. Petrenko Ukraine

- P. Prinetto Italy

- J. Raik Estonia

- A. Romankevich Ukraine

- A. Ryjov Russia R. Seinauskas – Lithuania

- S. Sharshunov Russia

- A. Singh USA

- J. Skobtsov Ukraine

- A. Stempkovsky Russia

- V. Tverdokhlebov Russia

- V. Vardanian Armenia

- V. Yarmolik Byelorussia

- E. J. Aas Norway

- J. Abraham USA

- M. Adamski Poland

- A . Barkalov Poland

- R. Bazylevych Ukraine

- V. Djigan Russia

- A. Drozd Ukraine

- W. Kuzmicz Poland

#### Organizing Committee

S. Chumachenko – Ukraine N. Kulbakova – Ukraine V. Obrizan – Ukraine A. Kamkin – Russia K.Petrosyanz – Russia A.Sokolov – Russia Y.Gubenko – Russia M.Chupilko – Russia E. Litvinova – Ukraine O. Guz – Ukraine G. Markosyan – Armenia

### **EWDTS CONTACT INFORMATION**

Prof. Vladimir Hahanov Design Automation Department Kharkov National University of Radio Electronics, 14 Lenin ave, Kharkov, 61166, Ukraine.

Tel.: +380 (57)-702-13-26 E-mail: hahanov@kture.kharkov.ua Web: www.ewdtest.com/conf/

## 7<sup>th</sup> IEEE EAST-WEST DESIGN & TEST SYMPOSIUM (EWDTS 2009)

Moscow, Russia, September 18-21, 2009

The main target of the **IEEE East-West Design & Test Symposium** (EWDTS) is to exchange experiences between scientists and technologies of Eastern and Western Europe, as well as North America and other parts of the world, in the field of design, design automation and test of electronic circuits and systems. The symposium is typically held in countries around the Black Sea, the Baltic Sea and Central Asia region. We cordially invite you to participate and submit your contribution(s) to EWDTS'09 which covers (but is not limited to) the following topics:

- Analog, Mixed-Signal and RF Test

- Analysis and Optimization

- ATPG and High-Level Test

- Built-In Self Test

- Debug and Diagnosis

- Defect/Fault Tolerance and Reliability

- Design for Testability

- Design Verification and Validation

- EDA Tools for Design and Test

- Embedded Software Performance

- Failure Analysis, Defect and Fault

- FPGA Test

- HDL in test and test languages

- High-level Synthesis

- High-Performance Networks and Systems on a Chip

- Low-power Design

- Memory and Processor Test

- Modeling & Fault Simulation

- Network-on-Chip Design & Test

- · Modeling and Synthesis of Embedded Systems

- · Object-Oriented System Specification and Design

- On-Line Testing

- Power Issues in Design & Test

- Real Time Embedded Systems

- Reliability of Digital Systems

- Scan-Based Techniques

- Self-Repair and Reconfigurable Architectures

- System Level Modeling, Simulation & Test Generation

- System-in-Package and 3D Design & Test

- Using UML for Embedded System Specification

- CAD and EDA Tools, Methods and Algorithms

- Design and Process Engineering

- Logic, Schematic and System Synthesis

- Place and Route

- Thermal, Timing and Electrostatic Analysis of SoCs and Systems on Board

- Wireless and RFID Systems Synthesis

- Digital Satellite Television

- Signal and Information Processing in RF and Communication

The symposium is organized by Kharkov National University of Radio Electronics, in cooperation with Tallinn University of Technology, Institute for System Programming of RAS, and Moscow Institute of Electronics and Mathematics. It is sponsored by the IEEE Computer Society Test Technology Technical Council (TTTC) and financially supported by Cadence, JTAG Technologies, Kaspersky Lab, Synopsys, Mentor Graphics, Tallinn Technical University, Donetsk Institute of Road Transport, Moscow Institute of Electronics and Mathematics, Virage Logic, Echostar, Aldec, Teprocomp, DataArt Lab.

#### CONTENTS

| Simulation-based Verification with APRICOT Framework using High-Level Decision Diagrams<br>Maksim Jenihhin, Jaan Raik, Anton Chepurov, Raimund Ubar13                                 |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Fault-Detection Capability Analysis of a Hardware-Scheduler IP-Core in Electromagnetic Interference Environment J. Tarrillo, L. Bolzani, F. Vargas, E. Gatti, F. Hernandez, L. Fraigi |

| Hardware Reduction in FPGA-Based Compositional Microprogram Control Units<br>Barkalov A.A., Titarenko L.A., Miroshkin A.N21                                                           |

| Optimization of Control Units with Code Sharing<br>Alexander A. Barkalov, Larisa A. Titarenko, Alexander S. Lavrik                                                                    |

| SAT-Based Group Method for Verification of Logical Descriptions with Functional Indeterminacy<br>Liudmila Cheremisinova, Dmitry Novikov                                               |

| MicroTESK: Automation of Test Program Generation for Microprocessors Alexander Kamkin                                                                                                 |

| Verification Methodology Based on Algorithmic State Machines and<br>Cycle-Accurate Contract Specifications<br>Sergey Frenkel and Alexander Kamkin                                     |

| Coverage Method for FPGA Fault Logic Blocks by Spares<br>Vladimir Hahanov, Eugenia Litvinova, Wajeb Gharibi, Olesya Guz43                                                             |

| Testing and Verification of HDL-models for SoC components<br>Vladimir Hahanov, Irina Hahanova, Ngene Christopher Umerah, Tiecoura Yves48                                              |

| The Model of Selecting Optimal Test Strategy and Conditions of ICs Testing During Manufacturing Sergey G. Mosin                                                                       |

| A Technique to Accelerate the Vector Fitting Algorithm for Interconnect Simulation<br>Gourary M.M., Rusakov S.G., Ulyanov S.L., Zharov M.M59                                          |

| Frequency Domain Techniques for Simulation of Oscillators<br>Gourary M.M., Rusakov S.G., Stempkovsky A.L., Ulyanov S.L., Zharov M.M                                                   |

| Distributed RLC Interconnect: Estimation of Cross-coupling Effects<br>H.J. Kadim, L.M. Coulibaly                                                                                      |

| Constrained-Random Verification for Synthesis: Tools and Results<br>D. Bodean, G. Bodean, O. Ghincul71                                                                                |

| Discussion on Supervisory Control by Solving Automata Equation<br>Victor Bushkov, Nina Yevtushenko, Tiziano Villa77                                                                   |

| Generalized Faulty Block Model for Automatic Test Pattern Generation<br>F. Podyablonsky, N. Kascheev                                                                                  |

| Self Calibration Technique of Capacitor`s Mismatching For 1.5 Bit Stage Pipeline ADC Vazgen Melikyan, Harutyun Stepanyan                                                              |

| Applied Library of Adaptive Lattice Filters for Nonstationary Signal Processing<br>Victor I. Djigan                                                                                   |

| On-chip Measurements of Standard-Cell Propagation Delay<br>S.O. Churayev, B.T. Matkarimov, T.T. Paltashev93                                                                           |

| FPGA FFT Implementation<br>S.O. Churayev, B.T. Matkarimov96                                                                                                                           |

| System Remote Control of the Robotized Complex - Pegas<br>Dmitry Bagayev, Evsyakov Artem                                                                                                                                                                                                                                                         | .200 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| Use of Predicate Categories for Modelling of Operation of the Semantic Analyzer of the Linguistic Processor<br>Nina Khairova, Natalia Sharonova                                                                                                                                                                                                  | .204 |

| Methodological Aspects of Mathematical Modelling of Processes in a Corporate Ecological System Kozulia T.V., Sharonova N.V.                                                                                                                                                                                                                      | .208 |

| Getting Optimal Load Distribution Using Transport-Problem-Based Algorithm<br>Yuri Ladyzhensky, Viatcheslav Kourktchi                                                                                                                                                                                                                             | 212  |

| Dialogue-based Optimizing Parallelizing Tool and C2HDL Converter<br>Steinberg B., Abramov A., Alymova E., Baglij A., Guda S., Demin S., Dubrov D., Ivchenko A.,<br>Kravchenko E., Makoshenko D., Molotnikov Z., Morilev R., Nis Z., Petrenko V., Povazhnij A.,<br>Poluyan S., Skiba I., Suhoverkhov S., Shapovalov V., Steinberg O., Steinberg R | .216 |

| The System for Automated Program Testing<br>Steinberg B., Alimova E., Baglij A., Morilev R., Nis Z., Petrenko V., Steinberg R                                                                                                                                                                                                                    | .218 |

| Development of the University Computing Network for Integrated Circuit Design<br>Atkin E., Volkov Yu., Garmash A., Klyuev A., Semenov D., Shumikhin V.                                                                                                                                                                                           | .221 |

| Increase in Reliability of On-Line Testing Methods Using Natural Time Redundancy<br>Drozd A., Antoshchuk S., Martinuk A., Drozd J                                                                                                                                                                                                                | .223 |

| An Algorithm of Carrier Recovery for Modem with M-ary Alphabets APK-Signals without PLL Victor V. Panteleev.                                                                                                                                                                                                                                     | .230 |

| At Most Attainable of Lengths a Symmetrical Digital Subscriber Line<br>on xDSL-technologies: Engineering-Maintenance Methods of the Calculation<br>Victor V. Panteleev, Nikolay I. Tarasov.                                                                                                                                                      | .234 |

| New Approach to ADC Design<br>Stanislav S. Gritsutenko                                                                                                                                                                                                                                                                                           | 240  |

| Simulation of Radiation Effects in SOI CMOS Circuits with BSIMSOI-RAD Macromodel K.O. Petrosjanc, I.A. Kharitonov, E.V. Orekhov, L.M. Sambursky, A.P. Yatmanov                                                                                                                                                                                   | .243 |

| Thermal Design System for Chip- and Board-level Electronic Components<br>K.O. Petrosjanc, I.A. Kharitonov, N.I. Ryabov, P.A. Kozynko                                                                                                                                                                                                             | .247 |

| TCAD Modeling of Total Dose and Single Event Upsets in SOI CMOS MOSFETs<br>K.O. Petrosjanc, I.A. Kharitonov, E.V. Orekhov, A.P. Yatmanov                                                                                                                                                                                                         | 251  |

| Reduction in the number of PAL Macrocells for Moore FSM implemented with CPLD<br>A. Barkalov, L. Titarenko, S. Chmielewski                                                                                                                                                                                                                       | 255  |

| Schematic Protection Method from Influence of Total Ionization Dose Effects<br>on Threshold Voltage of MOS Transistors<br>Vazgen Melikyan, Aristakes Hovsepyan, Tigran Harutyunyan                                                                                                                                                               | .260 |

| 5V Tolerant Power clamps for Mixed-Voltage IC's in 65nm 2.5V Salicided CMOS Technology<br>Vazgen Melikyan, Karen Sahakyan, Armen Nazaryan                                                                                                                                                                                                        | 263  |

| Analysis and Optimization of Task Scheduling Algorithms for Computational Grids<br>Morev N. V.                                                                                                                                                                                                                                                   | .267 |

| A Low Power and Cost Oriented Synthesis of the Common Model of Finite State Machine<br>Adam Klimowicz, Tomasz Grzes, Valeri Soloviev                                                                                                                                                                                                             | .270 |

|                                                                                                                                                                                                                                                                                                                                                  |      |

| Comparison of Survivability & Fault Tolerance of Different MIP Standards<br>Ayesha Zaman, M.L. Palash, Tanvir Atahary, Shahida Rafique275                                                   | 5 |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

| Hardware Description Language Based on Message Passing and Implicit Pipelining<br>Dmitri Boulytchev, Oleg Medvedev279                                                                       | 9 |

| V-Transform: An Enhanced Polynomial Coefficient Based DC Test for Non-Linear Analog Circuits<br>Suraj Sindia, Virendra Singh, Vishwani Agrawal                                              | 3 |

| GA-Based Test Generation for Digitally-Assisted Adaptive Equalizers in High-Speed Serial Links<br>Mohamed Abbas, Kwang-Ting (Tim) Cheng, Yasuo Furukawa,<br>Satoshi Komatsu, Kunihiro Asada | 7 |

| Between Standard Cells and Transistors: Layout Templates for Regular Fabrics<br>Mikhail Talalay, Konstantin Trushin, Oleg Venger                                                            | 3 |

| On-Chip Optical Interconnect: Analytical Modelling for Testing Interconnect Performance<br>H J Kadim                                                                                        | ) |

| The Problem of Trojan Inclusions in Software and Hardware<br>Alexander Adamov, Alexander Saprykin                                                                                           | 1 |

| Design methods for modulo 2n+1 multiply-add units<br>C. Efstathiou, I. Voyiatzis, M. Prentakis                                                                                              | 7 |

| Geometrical Modeling and Discretization of Complex Solids on the Basis of R-functions<br>Gomenyuk S.I., Choporov S.V., Lisnyak A.O                                                          | 3 |

| Selective Hardening: an Enabler for Nanoelectronics<br>Ilia Polian and John P. Hayes                                                                                                        | 6 |

| Parameterized IP Infrastructures for Fault-Tolerant FPGA-Based Systems: Development, Assessment, Case-Study<br>Kulanov Vitaliy, Kharchenko Vyacheslav, Perepelitsyn Artem                   | 2 |

| Generating Test Patterns for Sequential Circuits Using Random Patterns by PLI Functions<br>M. H. Haghbayan, A. Yazdanpanah, S. Karamati, R. Saeedi, Z. Navabi                               | 6 |

| A New Online BIST Method for NoC Interconnects<br>Elnaz Koopahi, Zainalabedin Navabi                                                                                                        | 2 |

| Low Cost Error Tolerant Motion Estimation for H.264/AVC Standard<br>M. H. Sargolzaie, M. Semsarzadeh, M. R. Hashemi, Z. Navabi                                                              | 5 |

| Method of Diagnosing FPGA with Use of Geometrical Images<br>Epifanov A.S                                                                                                                    | 0 |

| Performance Analysis of Asynchronous MIN with Variable Packets Length and Arbitrary Number of Hot-Spots<br>Vyacheslav Evgrafov                                                              | 4 |

| System in Package. Diagnosis and Embedded Repair<br>Vladimir Hahanov, Aleksey Sushanov, Yulia Stepanova, Alexander Gorobets                                                                 | 8 |

| Technology for Faulty Blocks Coverage by Spares<br>Hahanov Vladimir, Chumachenko Svetlana, Litvinova Eugenia,<br>Zakharchenko Oleg, Kulbakova Natalka                                       | 3 |

| The Unicast Feedback Models for Real-Time Control Protocol<br>Babich A.V., Murad Ali Abbas                                                                                                  | נ |

| Algebra-Logical Repair Method for FPGA Logic Blocks<br>Vladimir Hahanov, Sergey Galagan, Vitaliy Olchovoy, Aleksey Priymak                                                                  | 1 |

| The Method of Fault Backtracing for HDL - Model Errors Searching<br>Yevgeniya Syrevitch, Andrey Karasyov, Dariya Kucherenko                                                                  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Handling Control Signals for the Scan Technology<br>Olga Lukashenko, Dmitry Melnik, Vladimir Obrizan                                                                                         |

| Robust Audio Watermarking for Identification and Monitoring of<br>Radiotelephone Transmissions in the Maritime Communication<br>Vitaliy M. Koshevyy, Aleksandr V. Shishkin                   |

| An Interconnect BIST for Crosstalk Faults based on a Ring LFSR<br>Tomasz Garbolino, Krzysztof Gucwa, Andrzej Hławiczka, Michał Kopeć                                                         |

| Generation of Minimal Leakage Input Vectors with Constrained NBTI Degradation<br>Pramod Subramanyan, Ram Rakesh Jangir, Jaynarayan Tudu, Erik Larsson, Virendra Singh385                     |

| Very Large-Scale Intractable Combinatorial Design Automation Problems –<br>Clustering Approach for High Quality Solutions<br>Roman Bazylevych and Lubov Bazylevych                           |

| Flexible and Topological Routing<br>Roman Bazylevych and Lubov Bazylevych                                                                                                                    |

| An Algorithm for Testing Run-Length Constrained Channel Sequences<br>Oleg Kurmaev                                                                                                            |

| Constructing Test Sequences for Hardware Designs with Parallel Starting Operations Using Implicit FSM Models<br>Mikhail Chupilko                                                             |

| Redundant Multi-Level One-Hot Residue Number System Based Error Correction Codes<br>Somayyeh Jafarali Jassbi, Mehdi Hosseinzade, Keivan Navi                                                 |

| Parallel Fault Simulation Using Verilog PLI<br>Mohammad Saeed Jahangiry, Sara Karamati, Zainalabedin Navabi                                                                                  |

| IEEE 1500 Compliant Test Wrapper Generation Tool for VHDL Models<br>Sergey MIkhtonyuk, Maksim Davydov, Roman Hwang, Dmitry Shcherbin                                                         |

| Early Detection of Potentially Non-synchronized CDC Paths Using Structural Analysis Technique<br>Dmitry Melnik, Olga Lukashenko, Sergey Zaychenko411                                         |

| An Editor for Assisted Translation of Italian Sign Language<br>Nadereh Hatami, Paolo Prinetto, Gabriele Tiotto415                                                                            |

| Architecture Design and Technical Methodology for Bus Testing<br>M.H. Haghbayan, Z. Navabi                                                                                                   |

| Assertion Based Verification in TLM<br>AmirAli Ghofrani, Fatemeh Javaheri, Zainalabedin Navabi424                                                                                            |

| Flash-memories in Space Applications: Trends and Challenges<br>Maurizio Caramia, Stefano Di Carlo, Michele Fabiano, Paolo Prinetto                                                           |

| Design Experience with TLM-2.0 Standard: A Case Study of the IP Lookup LC-trie Application of Network Processor<br>Masoomeh Hashemi, Mahshid Sedghi, Morteza Analoui, Zainalabedin Navabi433 |

| Test Strategy in OSCI TLM-2.0<br>Mina Zolfy, Masoomeh Hashemi, Mahshid Sedghi, Zainalabedin Navabi and Ziaeddin<br>Daeikozekanani                                                            |

| Synthesizing TLM-2.0 Communication Interfaces<br>Nadereh Hatami, Paolo Prinetto                                                                                                              |

| Advanced Topics of FSM Design Using FPGA Educational Boards and Web-Based Tools<br>Alexander Sudnitson, Dmitri Mihhailov, and Margus Kruus446                                                      |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A Mixed HDL/PLI Test Package<br>Nastaran Nemati, Majid Namaki-Shoushtari, Zainalabedin Navabi                                                                                                      |

| Testing Methodologies on Communication Networks<br>Nadereh Hatami, Paolo Prinetto, Gabriele Tiotto, Paola Elia456                                                                                  |

| A Novel High Speed Residue to Binary Converter Design Based<br>on the Three-Moduli Set {2n, 2n+1+1, 2n+1-1}<br>Muhammad Mehdi Lotfinejad, Mohammad Mosleh and Hamid Noori                          |

| Performance Evaluation of SAT-Based ATPG on Multi-Core Architectures<br>Alejandro Czutro, Bernd Becker, Ilia Polian463                                                                             |

| Intelligent Testbench Automation and Requirements Tracking<br>Ivan Selivanov, Alexey Rabovoluk471                                                                                                  |

| Iterative Sectioning of High Dimensional Banded Matrices<br>Dmytro Fedasyuk, Pavlo Serdyuk, Yuriy Semchyshyn476                                                                                    |

| Estimating Time Characteritics of Parallel Applications in Technology of Orders<br>Based Transparent Parallelizing<br>Vitalij Pavlenko, Viktor Burdeinyi                                           |

| Phase Pictures Properties of Technical Diagnostics Complex Objects<br>Tverdokhlebov V.A                                                                                                            |

| Information Technology of Images Compression in Infocommunication Systems<br>Alexander Yudin, Natalie Gulak, Natalie Korolyova                                                                     |

| Technology of Cascade Structural Decoding<br>Leonid Soroka, Vladimir Barannik, Anna Hahanova490                                                                                                    |

| Technology of the Data Processing on the Basis of Adaptive Spectral-<br>Frequency Transformation of Multiadical Presentation of Images<br>Vladimir Barannik, Sergey Sidchenko, Dmitriy Vasiliev495 |

| Compression Apertures Method - Color Different Images<br>Konstantin Vasyuta, Dmitry Kalashnik, Stanislav Nikitchenko499                                                                            |

| Isotopic Levels Architectural Presentation of Images Relief<br>Vladimir Barannik, Alexander Slobodyanyuk502                                                                                        |

| Method and Mean of Computer's Memory Reliable Work Monitoring<br>Utkina T.Yu., Ryabtsev V.G                                                                                                        |

| Extended Complete Switch as Ideal System Network<br>Mikhail F. Karavay and Victor S. Podlazov                                                                                                      |

| Image Compression: Comparative Analysis of Basic Algorithms<br>Yevgeniya Sulema, Samira Ebrahimi Kahou                                                                                             |

| Networked VLSI and MEMS Designer for GRID<br>Petrenko A.I                                                                                                                                          |

| Path Delay Fault Classification Based on ENF Analysis<br>Matrosova A., Nikolaeva E                                                                                                                 |

| COMPAS – Advanced Test Compressor<br>Jiří Jeníček, Ondřej Novák                                                                                                                                    |

| INVITED TALKS                                                                                                                                                                                      |

| AUTHORS INDEX                                                                                                                                                                                      |

#### **Testing and Verification of HDL-models for SoC components**

Vladimir Hahanov, Irina Hahanova, Ngene Christopher Umerah, Tiecoura Yves Computer Engineering Faculty, Kharkov National University of Radioelectronics, Lenin Ave. 14, Kharkov, Ukraine, 61166, phone: (057) 70-21-421, (057) 70-21-326 E-mail: hahanov@kture.kharkov.ua; kiu@kture.kharkov.ua

#### Abstract

The testing and verification technology for system HDL models, focused to the significant improvement of the quality of design components for digital systems on chips and reduction the development time (time-tomarket) by using the simulation environment, testable analysis of the logical structure HDL-program and the optimal placement of assertion engine is proposed.

#### 1. Introduction

The novel testing and verification technology for system HDL models allows searching for errors in the HDL-code with a given thoroughness for an acceptable time by means of the introduction assertion redundancy to the critical points of the software model, which are defined by the synthesized logic functions of the testability. The controllability and observability criteria, used in hardware design and test, are applied to estimate the quality of software code in order to improve it and effective diagnose semantic errors.

The objective is improvement of the testing and verification technology for digital systems to diagnose and correct of errors for HDL-models by sharing of the assertion engine and testable design technologies.

The research tasks: 1. Design verification and testing environment for system HDL-model on the basis of assertions. 2. Development of testability evaluation metrics on the basis of new logic testability function. 3. Application of a technological assertion model to verify an IP-core filter on the basis of discrete cosine transform. 4. Practical results and directions for further research.

The research sources: 1. Technologies and tools of test and testbench creation are represented in the papers [1-3]. 2. Models and methods for verification of the system models on the basis of assertions are described in [4-7]. Testable software design uses the IEEE standards [8-10], as well as innovative solutions

to verify and testability analysis for the system HDL-models [11-18].

#### 2. Infrastructure of Design Verification

The verification model can be represented as a generalized equation for fault detection  $T \oplus S = L$  at the system level or more detail in the components:

$$(T,F) \oplus (S,A) = L_s$$

.

Here T, F are test patterns and functional coverage of the reference model with expected responses; S, A are testable HDL-model and assertion engine for the verification and exact diagnosis of errors in software code. Hardware testing is based on utilize the analytic expression  $(T) \oplus (S, B) = L_h$ , where B is the boundary scan register defined by the IEEE 1500 standard and used as a complement of the model to obtain the desired diagnosis thoroughness. At that  $L_s$ ,  $L_h$  are lists of errors and faults, obtained on the stages of design verification and product testing.

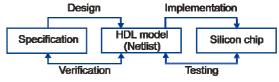

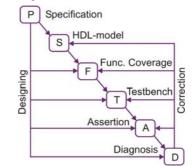

Verification and testing strategies have different models of technology application, focused to reduction of time-to-market. The iterative verification process seeks to correct the errors of system level HDL-model, obtained from the project specification (Fig. 1). The end result is a netlist or debugged HDL-model of register level. The subsequent iterative process is synthesis and implementation of a design in silicon chip. Here the testing checks the correction of hardware implementation for HDL-model to the register or gate level in an FPGA. For ASICs such technology would not be practical because the reprogramming of errors would cost up to one million dollars.

Fig. 1. Strategy of project designing

Taking into account the definitions and explanations model of the environment or macroprocess of verification for software stage of a project is focused to reduce the time of product creation and increase the yield for the use of code redundancy in the form of assertion engine and use testbench in conjunction with the metrics for determining the quality of the test or the functional completeness.

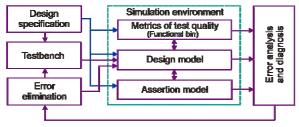

Testing and verification infrastructure for HDLmodel is shown in Fig. 2, where the specification of a design described in the formal high-level programming language, is the initial information for the follows: creation of the metrics for the estimation of test quality as functional coverage, HDL-model of a design, testbench, assertion structure that is complement to the basic model (it is necessary to accelerate testing and debugging of a design).

The verification environment is presented by simulation system (for instance, Questa, Mentor Graphics), test system (Testbench), assertion engine and system code of the model by using languages VHDL, Verilog, System Verilog. Testbench sets input stimuli and reference responses for them, defined in the HDL-languages, focused to functionality check (variables, functions, sequences), parameters of which are defined in a functional bin.

Assertion engine model redundancy. is complementary testbench to verify the time internal design status, represented by input-output assertions and designed to accelerate the testing, verification, diagnosis and correction of design errors in the system code. Assertions can be generated not only by specification, but also by HDL-model, removing the unnecessary construction, and the rest need to be modified to the assertion form. At the same time there is the probability of software error recurrence in an assertion, which will not be identified in the simulation.

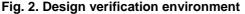

A simplified interaction structure for the assertion engine and other components of the verification and diagnosis environment is presented in Fig. 3. Testbench is a reference model of design object in the form of input and output responses. Often, already proven and accessible model of another company, which is checked on the Model Under Verification (MUV), is used instead of testbench. In this case, a generator of input sequences or testbench without output responses is required. Assertion Engine is a superstructure for the modules Testbench and MUV and it is designed to compare the simulation results in order to create a binary output response vector (assertion state vector):

## Fig. 3. Assertion utilize technology for design verification

Sequence of operations for creation the verification environment is interesting. Here sole argument is a design specification; all other is derivative from it. The interconnection structure for the design and diagnosis with subsequent correction of errors in the HDL-code is shown in Fig. 4.

Fig. 4. Design verification flow

## **3. Analytical Model of Verification Infrastructure**

For identification of a generalized state of HDLmodel the reference signatures are formed for critical points (variables, registers, memory) in time and space. Then the analysis of HDL-model for its diagnosis is performed by comparing the reference and experimental signatures to form the assertion vector describing the comparison state (reference and real) for the object components in time and space. It is advisable to form the assertion vector regardless of design HDL-model. Assertion and functional models are processed concurrently and independently of one another by simulation environment.

Assertion model determines the deviations from the behavior of the object in significant points of the space-time reference structure. The assertion format must conform to the format of the HDL-model. Assertions are focused to the diagnosis of semantic errors for HDL-model by means of Testbench and MUV.

The analytical model of the verification infrastructure is represented by the following expressions (P– design specification, S– soft-model, A– assertion model, T– Testbench, F– functional bin, D – module for error diagnosis and C – conditions for error diagnosis):

$$M = \{P, S, A, T, F, d, C\},$$

$$1) S = f_1(P) = |S_{ij}|;$$

$$2) F = f_2(P, S) = \{F_1, F_2, ..., F_i, ..., F_n\};$$

$$3) T = f_3(P, S, F) = \{T_1, T_2, ..., T_i, ..., T_n\};$$

$$4) A = f_4(P, S, F, T) = |A_{ij}|;$$

$$(1)$$

$$5) D = f_5(P, S, F, T, A) = |L_{ij}| \in \{L_s, L_h\};$$

$$6) C = [\bigcup_{i=1}^{n} F_i \in F = P] \land [\bigcup_{i=1}^{n} T_i \in T = F];$$

$$7) L_s = (T, F) \oplus (S, A);$$

$$8) L_h = (T) \oplus (S, B).$$

Here, the expression 6 defines the conditions of test confidence for functional bin concerning the specification. Line 7 defines the function of determination the design errors in the transition from the system level to register one, using all attributes of verification infrastructure. The function 8 regulates the detection of faults in operation stage of digital systemon-a-chip.

The assertion redundancy is a function of critical points of HDL-model, the maximum number of which may be equal to the number of time frames for functional components identified by the specification.

A priori, the coordinates of the assertion vector are assigned the value X. Then the critical coordinates are identified, a number of which would be sufficient to carry out a verification experiment in the search for faulty software blocks with specified diagnosis thoroughness. These coordinates are identified by the unities. In the process of simulation vector coordinates are modified to reduce the unities. Each coordinate of the vector A is in compliance with a list of all nodesancestors of software transaction graph. The reachability matrix of a transaction graph or lists of nodes- ancestors correspond to the vector coordinates.

For the actual binary state the elements of the vector A unconditional diagnosis procedure is performed for the list L to diagnose faulty software blocks d(A), defined by the following expressions [18]:

$$\begin{cases} L_{s}(A) = (\bigcap A_{i}) \setminus (\bigcup A_{i}); \\ \forall i(A_{i} = 1) \quad \forall i(A_{i} = 0) \end{cases} \\ L_{m}(A) = (\bigcup A_{i}) \setminus (\bigcup A_{i}). \\ \forall i(A_{i} = 1) \quad \forall i(A_{i} = 0) \end{cases}$$

(2)

The system of equations is to search for single and multiple errors by using the assertion state vector. The length of assertion vector is equal to the number of nodes in a graph or the number of program blocks in the functional-logical structure of HDL-code. Vector model for verification environment is presented below:

$$\begin{array}{c|c}

\hline T_1 \\

\hline T_2 \\

\hline T_i \\

\hline T_n

\end{array} \oplus

\begin{array}{c|c}

\hline S_1 \\

\hline S_2 \\

\hline S_n

\end{array} =

\begin{array}{c|c}

\hline A_1 \\

\hline A_2 \\

\hline A_i \\

\hline A_n

\end{array}

\begin{array}{c|c}

d \\

\hline L_1 \\

\hline L_2 \\

\hline L_i \\

\hline L_n

\end{array}$$

(3)

In the simulation the comparison of responses for testbench and HDL-model is carried out; it forms the coordinate states of assertion vector.

$$A_i = f(T_i, S_i) = T_i \oplus S_i, A_i = \{0, 1, X\}.$$

Then, essential (0,1)- coordinates of an assertion vector mask a reachability matrix for obtaining a list of program blocks with errors by performing one of the procedures set out in (2).

#### 4. Testability analysis for software HDLmodels

Substantial redundancy of the HDL-model assumes its efficient use in order to improve testability of structure for designed code.

Existing standards for hardware testable design can be adapted to verify the HDL-code of system and register software models. S.G. Sharshunov's register or transaction transfer graph that provides information about interrelations between Boolean and register variables, memory and interface buses, can be used. This data can be obtained automatically, by analyzing the syntax of HDL-code lines. Generated graph should cover the functionalities of the software model components and define all the existing links for the reception, transmission and transformation of information between the nodes of a transaction graph (TG). For integral estimating the testability Q of transaction graph the following criteria are introduced:

$$Q = \frac{Z(S)}{Z(S) + Z(F) + Z(T) + Z(A)} \times \frac{1}{n} \sum_{i=1}^{n} (U_i \times N_i);$$

$$U_i = \frac{1}{T} \sum_{j=1}^{x_i} T_j^i \times \frac{1}{d_i^x \vee t_i^x}; \quad N_i = \frac{1}{T} \sum_{j=1}^{y_i} T_j^i \times \frac{1}{d_i^y \vee t_i^y}.$$

(4)

Controllability and observability is the metrics for testability estimation not interconnections, but components of HDL-code, such as: registers, counters, memory or arrays, input-output buses, vectors, logical or arithmetic variables. These characteristics have a functional dependence on the structural granularity of a component (relative to the inputs) or the length of conjunctive term –  $d_i^x \vee t_i^x$ , ( $d_i^y \vee t_i^y$  – relative to the outputs), as well as on the percentage of the command quantity  $\frac{1}{T} \sum_{j=1}^{x_i} T_j^i$ , having input (output –  $\frac{1}{T} \sum_{j=1}^{y_i} T_j^i$ )

access to a node at the analysis of the software. Testability Q, presented in (4), depends on the controllability U, observability N, as well as model redundancy (Z) provided by the components: metrics of the functional coverage (F), testbench (B), assertion engine (A). The controllability (observability) is a function of the number of operators, incoming into the node (outcoming from the node) of a transaction graph, as well as the structural granularity of the element – the distance from the inputs (outputs) or the number of time cycles, required for the component control (observation) in given state in the time axis.

This testability criterion can also be used to estimate the quality of the control flow graph for computational processes. Only the statement nodes, loaded with the input conditions, as well as the node position relative to the beginning or the end of control circuit are considered. The position of the statement node is correlated with control cycle of computational process. Number of conditions for the execution of an operation set at each node, joint by operation Or, increases the testability of a graph in controllability. Similarly the observability is determined, on which affect not only the structural granularity, but the power of conditions, created by the functional operations And, Or. The testability of a node for oriented graph may be described by logical function, defined as a conjunctive normal form CNF. At that the testability (controllability and observability) will be determined by Quine estimation of CNF computational complexity. In general, the logic functions of controllability and observability for current node of the transaction graph are determined by conjunction of the disjunctive terms – the first line of (5):

1)

$$U_{r}^{f} = {}^{n_{r}^{x}}_{\Lambda(\bigvee} T_{rij}^{x}); N_{r}^{f} = {}^{n_{r}^{y}}_{\Lambda(\bigvee} T_{rij}^{y});$$

$i=1 \ j=1 \$

Here the controllability  $U_r^f$  (observability  $N_r^f$ ) function is determined by conjunction of all nodesancestors  $n_r^x$  (successors  $n_r^y$ ), where each of them have  $x_i$  incoming ( $y_i$  outgoing) arcs-transactions connected by disjunction signs.

The power of disjunctive terms corresponds to the number of arcs incoming into the node, but the number of conjunctions is the structural granularity of the component location.

Then the conjunctive form is transformed to DNF – the second line of (5), where the number of terms for the controllability (observability) function  $x_r(y_r)$  is equal to all possible ways of forming the state for a node, and the length of controllability (observability) term  $n_i^x(n_i^y)$  is a condition for the reachability of a node – the structural granularity from the inputs (outputs).

The interesting solution when the controllability and observability for the current node of transaction graph is determined on the basis of the logical functions of the observability and controllability  $(U_i, N_i)$  and the integral testability estimation (Q), when using the apparatus – the algebraic form of graph representation [18]. The formulas for calculating these criteria are the following:

$$U_{i} = \frac{1}{t_{max}^{x} \times n_{t}^{x}} \times \sum_{i=1}^{n_{t}^{x}} (t_{max}^{x} - |t_{ij}^{x}| + 1);$$

$$N_{i} = \frac{1}{t_{max}^{y} \times n_{t}^{y}} \times \sum_{i=1}^{n_{t}^{y}} (t_{max}^{y} - |t_{ij}^{y}| + 1);$$

$$Q = \frac{1}{n} \sum_{i=1}^{n} (U_{i} \times N_{i}),$$

(6)

where  $t_{max}^{x}, n_{t}^{x}, k_{i}^{x}, \left| t_{ij}^{x} \right|$  are the conjunctive term of maximum length for determining the controllability criterion; a number of terms in a logical controllability function; a number of transactions (letters) in current function term; power of the transaction in a term. Similar designations are used for calculating the observability criterion for each node of transaction graph –  $t_{max}^{y}, n_{t}^{y}, k_{i}^{y}, \left| t_{ij}^{y} \right|$ .

#### 5. Verification of DCT IP-core, Xilinx

The proposed verification models for software HDLcode are tested on a real project Xilinx IP-core in order to determine the presence of errors. At that the positive result about the semantics of the program is obtained for subsequent correction of the code. Fragment of the discrete cosine transform module is presented in Listing 1 [Xilinx.com]. The whole HDL-model consists of 900 lines of System Verilog code.

Listing 1. module Xilinx `timescale 1ns/10ps module dct ( CLK, RST, xin,dct\_2d,rdy\_out); output [11:0] dct\_2d; input CLK, RST; input[7:0] xin; /\* input \*/ output rdy\_out; wire[11:0] dct\_2d;

/\* The first 1D-DCT output becomes valid after 14 +64 clk cycles. For the first 2D-DCT output to be valid it takes 78 + 1clk to write into the ram + 1clk to write out of the ram + 8 clks to shift in the 1D-DCT values + 1clk to register the 1D-DCT values + 1clk to add/sub + 1clk to take compliment + 1 clk for multiplying + 2clks to add product. So the 2D-DCT output will be valid at the 94th clk. rdy\_out goes high at 93rd clk so that the first data is valid for the next block\*/ Endmodule

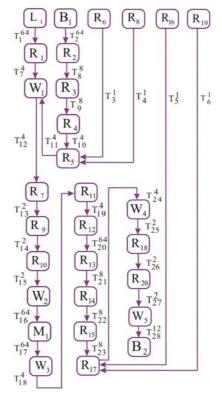

In accordance with the rules of testability analysis described above, the transaction graph is designed presented in Fig. 5, which for the module Xilinx has 28 nodes-components (input and output buses, logic and register variables, vectors and memory).

Arc identifier has the upper index meaning the number of transactions in the program between the outcoming and incoming nodes. For each node the logical function of controllability and observability are constructed. Example of the controllability function for the node  $B_2$  is the following:

$$B_{2} = T_{28}^{12} T_{27}^{2} T_{22}^{2} T_{25}^{2} T_{24}^{4} (T_{5}^{1} \vee T_{6}^{1} \vee T_{7}^{1} \vee T_{12}^{1} T_{13}^{2} T_{14}^{2} T_{15}^{2} T_{15}^{64} T_{17}^{64} T_{18}^{4} T_{19}^{4} T_{20}^{64} T_{21}^{8} T_{22}^{8} \vee T_{12}^{1} T_{13}^{12} T_{15}^{12} T_{15}$$

$$\wedge T_{23}^{8} (T_{1}^{64}T_{7}^{4} \vee T_{11}^{4}T_{2}^{64}T_{8}^{8}T_{9}^{9}T_{10}^{4} \vee T_{11}^{4}T_{3}^{1} \vee T_{11}^{4}T_{4}^{1})) =$$

$$= T_{28}^{12}T_{27}^{2}T_{22}^{2}T_{25}^{2}T_{24}^{4}T_{5}^{1} \vee T_{6}^{1}T_{28}^{2}T_{27}^{2}T_{22}^{2}T_{25}^{2}T_{24}^{4} \vee$$

$$\vee T_{28}^{12}T_{27}^{2}T_{22}^{2}T_{25}^{2}T_{24}^{4}T_{12}^{4}T_{13}^{2}T_{14}^{2}T_{15}^{2}T_{15}^{64}T_{17}^{64}T_{18}^{4} \wedge$$

$$\wedge T_{19}^{4}T_{20}^{64}T_{21}^{8}T_{22}^{8}T_{23}^{8}T_{1}^{64}T_{7}^{4} \vee$$

$$\vee T_{28}^{12}T_{27}^{2}T_{22}^{2}T_{25}^{2}T_{24}^{4}T_{12}^{4}T_{13}^{2}T_{14}^{2}T_{15}^{2}T_{15}^{64}T_{17}^{64} \wedge$$

$$\wedge T_{18}^{4}T_{19}^{4}T_{20}^{64}T_{21}^{8}T_{22}^{8}T_{23}^{8}T_{11}^{4}T_{2}^{64}T_{8}^{8}T_{9}^{8}T_{10}^{4} \vee$$

$$\vee T_{11}^{4}T_{3}^{1}T_{28}^{12}T_{27}^{2}T_{22}^{2}T_{25}^{2}T_{24}^{4}T_{12}^{4}T_{13}^{2}T_{13}^{2}T_{14}^{2}T_{15}^{2} \wedge$$

$$\wedge T_{15}^{64}T_{17}^{64}T_{18}^{4}T_{19}^{4}T_{20}^{64}T_{21}^{8}T_{22}^{8}T_{23}^{8} \vee$$

$$\vee T_{11}^{4}T_{4}^{1}T_{28}^{12}T_{27}^{2}T_{22}^{2}T_{25}^{2}T_{24}^{4}T_{12}^{4}T_{13}^{2}T_{14}^{2}T_{15}^{2} \wedge$$

$$\wedge T_{15}^{64}T_{17}^{64}T_{18}^{4}T_{19}^{4}T_{20}^{64}T_{21}^{8}T_{22}^{8}T_{23}^{8} \vee$$

$$\wedge T_{15}^{15}T_{17}^{64}T_{18}^{4}T_{19}^{4}T_{20}^{64}T_{21}^{8}T_{22}^{8}T_{23}^{8} \wedge$$

$$\wedge T_{15}^{2}T_{15}^{64}T_{17}^{64}T_{18}^{4}T_{19}^{4}T_{20}^{64}T_{21}^{8}T_{22}^{8}T_{23}^{8} .$$

#### Fig. 5. Transaction graph for Xilinx model

For the node  $L_1$  DNF of observability function is presented in the following form:

$$\begin{split} N(L_1) &= T_{28}^{12} T_{27}^2 T_{22}^2 T_{25}^2 T_{24}^4 T_{23}^8 T_{22}^8 T_{21}^8 T_{20}^{64} T_{19}^4 T_{18}^4 T_{17}^{64} \wedge \\ & \wedge T_{16}^{64} T_{15}^2 T_{14}^2 T_7^4 T_1^{64}. \end{split}$$

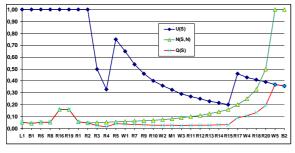

The result of calculating the controllability, observability and testability for the graph (Fig. 5) is shown in Fig. 6.

Fig. 6. Testability curve for Xilinx model

determination of controllability After and observability for transaction graph nodes the calculation of the generalized testability criterion for each component of software code is carried out in accordance with expression (6). For the Xilinx model such estimation is equal to 0,382. It describes the quality of the design variant, which is very important when comparing several alternative solutions. As an example of the positive use of developed models and methods the testability analysis for software code of discrete cosine transform from the Xilinx library is performed. It was done construction of transaction model, calculation of the testability characteristics, and identification of critical points.

#### 6. Conclusion

1. An universal model of software component in the form of transaction graph, which can be used to solve the problems of testability analysis in order to obtain the required diagnosis granularity for HDL-code is presented.

2. The logic testability functions for HDL-models on the basis of transaction graph are proposed in order to determine the testability estimates (controllability and observability) for software components and HDLdesign as a whole.

3. Examples and testability curves (controllability and observability) for software models represented by transaction graphs are made.

4. The practical significance of the proposed methods and models is the market appeal and high interest from the technology companies to the innovation solutions of the effective testing and verification of hardware and software components for system-level design in order to reduce time-to-market and raise yield. 5. Further research will be focused on the development of standard interfaces for integration of models, methods and software in the technological design flows of digital systems on chips.

#### 7. References

- Abramovici M., Breuer M.A. and Friedman A.D. Digital System Testing and Testable Design. Computer Science Press.- 1998.- 652 p.

- [2] Bayraktaroglu Ismet, Orailoglu Alex. The Construction of Optimal Deterministic Partitionings in Scan-Based BIST Fault Diagnosis: Mathematical Foundations and Cost-Effective Implementations // IEEE Transactions on Computers.- 2005.- P.61-75.

- [3] Douglas Densmore, Roberto Passerone, Alberto Sangiovanni-Vincentelli. A Platform-Based taxonomy for ESL Design // Design&Test of computers.-September-October, 2006.-P. 359-373.

- [4] Francisco DaSilva, Yervant Zorian, Lee Whetsel, Karim Arabi, Rohit Kapur. Overview of the IEEE P1500 Standard // ITC International Test Conference. 2003. P.988–997.

- [5] Rashinkar P., Paterson P., Singh L. System-on-chip Verification: Methodology and Techniques.-Kluwer Academic Publishers.- 2002.- 324 p.

- [6] Zorian Yervant. What is Infrustructure IP? // IEEE Design & Test of Computers.- 2002.- P. 5-7.

- Zorian Yervant, Gizopoulos Dmytris. Gest editors' introduction: Design for Yield and reliability // IEEE Design & Test of Computers.- 2004.- P. 177-182.

- [8] Zorian Yervant. Guest Editor's Introduction: Advances in Infrastructure IP // IEEE Design and Test of Computers.-2003.-49 p.

- [9] Thatte S.M., Abraham J.A. Test generation for microprocessors // IEEE Trans. Comput.- 1980.- C-29. No 6.- P. 429-441.

- [10] Sharshunov S.G. Test Genagation for Microprocessors. 1. General Model. Check of data processing // Automation and Telemechanics.-1985.-№11.-P.145-155.

- [11] Jerraya A.A. System Level Synthesis SLS. TIMA Laboratory. Annual Report. – 2002. – P. 65-75.

- [12] Frank Ghenassia. Transaction Level Modeling with SystemC. TLM Concepts and Applications for Embedded Systems. Published by Springer.– 2005.– 282 p.

- [13] Bergeron, Janick. Writing testbenches: functional verification of HDL models.– Boston: Kluwer Academic Publishers.– 2001.– 354 p.

- [14] Janick Bergeron, Eduard Cerny, Alan Hunter, Andrew Nightingale. Verification Methodology. Manual for SystemVerilog.- Springer.- 2005.- 528 p.

- [15] Harry Foster, Adam Krolnik, David Lacey. Assertion-based design.– Second edition.– Kluwer Academic Publishers.– Springer.– 2005.– 392 p.

- [16] Rashinkar P., Paterson P., Singh L. System-on-chip Verification: Methodology and Techniques.- Kluwer Academic Publishers.-2002.- 393 p.

- [17] Meyer A.S. Principles of Functional Verification. Elsevier Science.- 2004.-206 p.

- [18] Hahanov V.I., Litvinova E.I., Guz O.A. Design and Testing of Digital System-on-Chip.- Kharkov: KHNURE.- 2009.-484 p.

Camera-ready was prepared in Kharkov National University of Radio Electronics by Dr. Svetlana Chumachenko Lenin ave, 14, KNURE, Kharkov, 61166, Ukraine

> Approved for publication: 31.08.2009. Format 60×841/8. Relative printer's sheets: . Circulation: 150 copies. Published by SPD FL Stepanov V.V. Ukraine, 61168, Kharkov, Ak. Pavlova st., 311

Матеріали симпозіуму «Схід-Захід Проектування та Діагностування – 2009» Макет підготовлено у Харківському національному університеті радіоелектроніки Редактори: Володимир Хаханов, Світлана Чумаченко Пр. Леніна, 14, ХНУРЕ, Харків, 61166, Україна

> Підписано до публікації: 31.08.2009. Формат 60×84<sup>1</sup>/<sub>8</sub>. Умов. друк. арк. . Тираж: 150 прим. Видано: СПД ФЛ Степанов В.В. Вул. Ак. Павлова, 311, Харків, 61168, Україна