Изобретение относится к области вычислительной техники, системам технического зрения, тренажерам различного назначения, а так же может быть использовано в телевизионной технике.

Известно устройство преобразования координат для геометрической коррекции изображений, содержащее четыре управляемых делителя, два элемента ИЛИ, два реверсивных счетчика и блок синхронизации [1].

Недостатком устройства является крайне ограниченный набор геометрических преобразований: поворот и смещение точки в декартовой системе координат в плоскости изображения, а также невозможность выполнять преобразования в реальном масштабе времени.

Наиболее близким по технической реализации предлагаемому изобретению явпяется устройство для формирования динамических изображений, содержащее блок задания входных синхронизации, два параметров и преобразования координат (ВПК), формирователь управляющих импульсов, шины управляющего и выходного сигналов. Недостатком устройства является также минимальный набор геометрических преобразований (афинные) [2].

Целью изобретения является устройство вычислений с расширенными возможностями геометрических преобразований (афинных и центропроективных) плоского изображения в реальном масштабе времени, обеспечивающее высокое качество изображения с большой глубиной масштабирования и высоким угловым разрешением.

Указанная цель достигается тем, что в устройство, содержащее блок задания входных параметров, два блока преобразования координат, блок памяти и блок управления, блока памяти причем выхол явпяется информационным входом устройства, введены третий блок преобразования координат, три логарифмических преобразователя, два функциональных преобразователя, два адресных формирователя, блок формирования линии бесконечно удаленных точек, выход которого явпяется выходом формирования горизонта устройства, с первого по третий управляющие выходы блока задания входных параметров соединены с входами сигналов сопровождения соответственно с первого по тертий кодов параметров направляющих косинуса первого. второго третьего блоков И преобразования координат, входы разрешения записи которых соединены с входами разрешения записи первого и второго алресных преобразователей и четвертым управляющим выходом блока задания входных параметров, первый информационный выхол которого соелинен С входами кода параметра направляющей косинуса первого, второго и третьего блоков преобразования координат. информационные входы которых соединены с информационными входами первого, второго и третьего логарифмических преобразователей соответственно, синхровходы которых соединены с первыми синхровходами первого, второго и третьего блоков преобразования координат, первого синхровходами второго и функциональных преобразователей, первого и второго адресных преобразователей, блока

формирования линии бесконечно удаленных точек и первым входом блока управления, второй выход которого соединен со вторыми синхровходами первого, второго и третьего блоков преобразования первые входы сброса координат. соединены с третьим входом блока управления, со входами сброса первого, второго и третьего логарифмических преобразователей, первого и второго функциональных преобразователей, блока формирования линии бесконечно удаленных точек, первыми входами сброса первого и второго адресных преобразователей, вторые входы сброса которых соединены со вторыми входами сброса трех блоков преобразования координат и с четвертым входом блока управления, пятый выход которого соединен с входом блока задания входных параметров, вторые информационные входы которого соединены с входами кодов порядка и мантиссы первого и второго адресных формирователей, входы которых соединены с первым и вторым адресными входами блока памяти, пятый и шестой управляющие входы блока задания входных параметров соединены с входами сигналов сопровождения кода порядка и кода мантиссы соответственно первого и второго адресных формирователей, первый и второй выходы первого и третьего логарифмических преобразователей соединены с входами целой и дробной части первого операнда соответственно первого И второго функциональных преобразователей, входы целой и дробной части второго операнда первого и огодота функциональных преобразователей соединены с первым вторым выходами второго логарифмического преобразователя, первый и второй выходы первого и второго функциональных преобразователей соединены с входами первого и второго операндов соответственно первого и адресных формирователей, второго знакового разряда первого и третьего блоков преобразования координат соединены с входами знака первого операнда первого и второго адресных формирователей соответственно, выход знакового разряда второго блока преобразования координат соединен с входами знака второго операнда первого второго адресных И формирователей, информационный вход блока формирования линии бесконечно удаленных точек соединен с информационным выходом второго блока преобразования координат.

R предлагаемом устройстве координат преобразования солержит комбинационный сумматор, первую, и вторую схему ИЛИ, элемент НЕ, комбинационный узел, элемент задержки, а также первый, второй, третий и четвертый регистры, причем первый синхровход блока соединен с первым входом первого элемента ИЛИ, выход которого соединен с входом разрешения записи первого регистра, информационный вход которого соединен с информационным входом второго регистра и выходом комбинационного сумматора. первый информационный вход которого через монтажное ИЛИ соединен с выходами первого и второго регистров и информационным выходом блока, выходы третьего и четвертого регистров через ИЛИ соединены вторым монтажное CO информационным входом комбинационного сумматора, вход кода параметра направляющей косинуса блока соединен с информационными входами третьего и четвертого регистров, входы разрешения записи которых соединены с одноименным входом блока и с первым входом комбинационного узла, первый вход сброса блока соединен с входом установки в ноль первого регистра, вход запрещения выходов которого соединен с одноименным входом трељего регистра и выходом элемента НЕ, вход которого соединен с входами запрещения выходов второго четвертого регистров, вторым входом комбинационного узла и вторым синхровходом блока, вход сигнала сопровождения первого параметра направляющей косинуса которого соединен с третьим входом комбинационного узла и первым входом второго элемента ИЛИ, второй вход которого соединен с входом сигнала сопровождения третьего параметра направляющей косинуса блока, вход сигнала сопровождения второго параметра направляющей соединен с четвертым косинуса комбинационного узла и входом разрешения приема четвертого регистра, вход установки в ноль которого соединен с одноименными входами второго и третьего регистров и вторым входом сброса блока, выход комбинационного узла соединен с входом элемента задержки, выход которого соединен со вторым входом первого элемента ИЛИ и входом разрешения записи второго регистра, выход второго элемента ИЛИ соединен с входом разрешения приема третьего регистра, выход знакового разряда соединен через монтажное ИЛИ с выходами старших разрядов первого и второго регистров.

Преобразователь логарифмический содержит входной регистр, два промежуточных регистра, блок управления сдвигом, блок сдвига аргумента, блок задержки, блок памяти, блок элементов НЕ и сумматор, комбинационный информационный вход преобразователя соединен с информационным входом входного регистра, выход которого соединен с информационным входом блока сдвига аргумента и входа блока управления сдвигом, выход которого соединен с информационным входом блока задержки и с входом блока управления сдвигом аргумента, выход которого соединен с информационным входом первого промежуточного регистра, выход которого соединен с адресным входом блока выход которого соединен памяти. информационным входом второго промежуточного регистра, выходы опорного значения функции логарифма и поправки которого соединены соответственно с первым и вторым информационными входами комбинационного сумматора, выход которого является первым выходом преобразователя, вторым выходом которого является выход блока элементов НЕ, вход которого соединен с выходом блока задержки, вход установки в ноль которого соединен с одноименными входами первого и второго промежуточного регистров, входного регистра и входом сброса преобразователя, синхровход которого соединен с синхровходами входного регистра и первого и второго промежуточных регистров.

Функциональный преобразователь содержит четыре регистра, блок памяти, два комбинационных сумматора, причем входы целой части первого и второго операндов преобразователя соединены с первым и третьим

информационными входами первого комбинационного сумматора, второй и четвертый информационные входы которого соединены с первого И второго регистров. выходами информационные входы которых соединены с входами дробной части первого и второго операндов преобразователя, синхровход которого соединен с входами разрешения записи первого, второго, третьего и четвертого регистров, входы установки в ноль которых соединены с входом сброса преобразователя, выход дробной части первого комбинационного сумматора соединен с информационным входом третьего регистра, выход которого соединен с адресным входом блока выход которого ∞единен информационным входом четвертого регистра, выходы функции и поправки которого соединены с первым и вторым информационными входами второго комбинационного сумматора, соединен С первым которого выходом преобразователя, второй выход которого соединен с выходом целой части первого комбинационного сумматора.

Адресный формирователь содержит семь регистров, блок сдвига, узел формирования знака, узел задержки, два комбинационных сумматора, причем вход первого, операнда формирователя соединен с информационным входом первого регистра, выход которого соединен информационным входом блока сдвига, а вход управления сдвигом которого соединен с выходом второго регистра, выходы третьего и четвертого регистров соединены с первым и вторым информационными входами комбинационного сумматора, выход которого соединен с информационным входом пятого выход которого соединен регистра. информационным входом второго регистра, вход которого разрешения записи ∞единен одноименными входами узла задержки первого, шестого, пятого и третьего регистров и входом синхронизации формирователя, первый вход сброса которого соединен с входами установки в ноль первого, второго, третьего, пятого и шестого регистров и узла задержки, информационный вход которого соединен с выходом узла формирования знаков, первый и второй входы которого соединены с входами знаков первого и второго операндов формирователя, вход второго операнда которого соединен с информационным входом третьего регистра, вход кода параметра и мантиссы формирователя соединен с информационными входами четвертого и седьмого регистров, входы разрешения записи которых соединены с входом разрешения записи формирователя, второй вход сброса которого соединен с входами установки в ноль четвертого и седьмого регистров, входы сигналов сопровождения кода порядка и кода мантиссы преобразователя соединены с входами разрешения приема четвертого и седьмого регистров соответственно, выход блока сдвига соединен с информационным входом шестого регистра, выходы шестого и седьмого регистров соединены с первым и вторым информационными входами второго комбинационного сумматора, третий информационный вход которого соединен с выходом узла задержки, выход комбинационного сумматора является выходом формирователя.

Блок формирования линии бесконечно

удаленных точек содержит входной регистр, дешифратор нуля и узел задержки, выход которого является выходом блока, информационный вход которого соединен с информационным входом входного регистра, выход которого соединен с входом дешифратора которого нуля. выход соединен информационным входом узла задержки, вход разрешения записи которого соединен одноименным входом входного регистра и входом синхронизации блока, вход сброса которого соединен с входом установки в ноль входного регистра и узла задержки.

управления Блок содержит синхронизации, триггер, два элемента задержки, три узла формирования импульсов и элемент И, причем первый вход узла синхронизации соединен с тактовым входом триггера, выход которого является первым выходом блока, второй выход узла синхронизации соединен с входом установки в ноль триггера, с входами первых элементов задержки, и узла формирования импульсов, третий выход узла синхронизации соединен с входами вторых узла формирования импульсов и элемента задержки, выход первого элемента задержки соединен с входом третьего узла формирования импульсов; выход которого является вторым выходом блока, третьим выходом которого является выход первого узла формирования импульсов, первый выход второго узла формирования импульсов соединен с четвертым выходом блока, пятый выход которого соединен с выходом элемента И, первый и второй входы которого соединены со вторым входом второго узла формирования импульсов и второго элемента задержки соответственно.

Анализ известных технических решений в исследуемой области позволяет сделать вывод об отсутствии в них признаков, сходных с существенными отличительными признаками в заявляемом изобретении, что позволяет сделать вывод о соответствии критерию "существенные отличия".

Для построения изображения в реальном масштабе времени требуется обеспечить проведение центропроективного преобразования, сводящегося к вычислению координат проекции элемента экрана на предметную плоскость. известных соотношений центропроективных преобразований (Четверухин Н.Ф. Проективная геометрия. Министерство просвещения РСФСР. - М., 1961. - 360с.) показал, что для проведения вычислений в реальном масштабе времени с заданной глубиной требуемым угловым масштабирования И разрешением необходимо преобразовать эти соотношения к виду:

$$X=X_{0}-Y_{0}\frac{S_{11}X_{9}+S_{12}Z_{9}+S_{13}}{S_{31}X_{9}+S_{32}Z_{3}+S_{33}}, \quad (1)$$

$$Z = Z_0 - Y_0 \frac{S_{21} X_9 + S_{22} Z_9 + S_{23}}{S_{31} X_9 + S_{32} Z_3 + S_{33}}, \quad (2)$$

где  $X_0, Z_0, Y_0$  - координаты центра проекции в декартовой "земной" системе координат;  $S_{IJ}$  - направляющие косинусы для связанной с летательным аппаратом системы координат (Доброленский Ю.П. и др. Автоматика управляемых снарядов. - М.: Оборониз, 1963. - 548с.);  $X_{21}, Z_{32}$  - текущие координаты экрана,

формируемые в процессе развертки телевизионного растра.

Структура соотношений (1, 2) обеспечивает достижение поставленной цели, т.к. известные формулы центропроективных преобразований представлены таким образом, что, во-первых, из общего набора параметров выделены "медленные"

параметры: X<sub>0</sub>, Z<sub>0</sub>, Y<sub>0</sub>, S<sub>ij</sub>, постоянные в пределах одного кадра изображения, вычисление которых осуществляется минимальными средствами универсальной вычислительной техники (микро-ЭВМ), а, следовательно, и стоимости: а также "быстрые" параметры: дроби в формулах (1, 2), которые вычисляются в темпе прорисовки отдельных пикселов с помощью спецпроцессора согласно предлагаемому изобретению. Во-вторых, в них выделены члены, требования к точности вычисления которых, исходя из общих требований к качеству изображения, оказываются различными.

Так величины Xo, Zo, Yo и Sij для обеспечения большого объема пространства при маневрировании летательного аппарата с требуемой точностью следует брать с большим числом разрядов (20 - 24 разряда). В то же время вычисление наиболее трудоемкой и длинной во времени операции деления возможно вести с относительной точностью 2-13, соответствующей угловому разрешению глаза.

Для решения поставленной задачи с помощью обычной ЭВМ понадобилась бы мощность ЭВМ порядка 0,5млд, операций в с., что соответствует параметрам наиболее мощных и дорогостоящих супер-ЭВМ.

Из формул (1 и 2) получим выражения для координат проекции элемента экрана на предметную плоскость, которые реализуются спецпроцессором. Для этого соотношения (1 и 2) преобразуем к виду:

$$X=X_0-2^{Py_0}2^{log_{2a}-log_{2b}}$$

(3)

$$Z = Z_0 - 2^{P_{y_0}} 2^{\log_2 c} - \log_2 b$$

(4)

где  $\mathbf{a.\,c}$  - числители,  $\mathbf{a.\,s}$  - знаменатель дробей выражений (1, 2),  $\mathbf{p_{yo}}$  - двоичный порядок  $\mathbf{yo}$  (мантисса  $\mathbf{yo}$  введена в коэффициенты  $\mathbf{SIJ}$  дробей выражений (1, 2)). Значение функции логарифма числа  $\mathbf{e}$  может быть вычислено следующим образом

$$\log_2(e) = d_e + \log_2 e_m \tag{5}$$

где  $d_e$  - целая часть логарифма,  $e_m$  - дробная часть числа  $e_{\centerdot}$

В этом случае очевидным являются следующие преобразования:

$$2^{\log_2 a - \log_2 b} = 2^d 2^k$$

, (6)

где  ${f d}$  - целая часть,  ${f k}$  - дробная часть разности логарифмов.

Окончательно соотношения (3 и 4) представим следующим образом:

$$X=X_0-2^{Py_0}+d_X 2^{K_X}$$

(7)

$Z=Z_0-2^{Py_0}+d_Z 2^{K_Z}$

Структура спецпроцессора фактически отражает структуру соотношений (7 и 8) центропроективных преобразований.

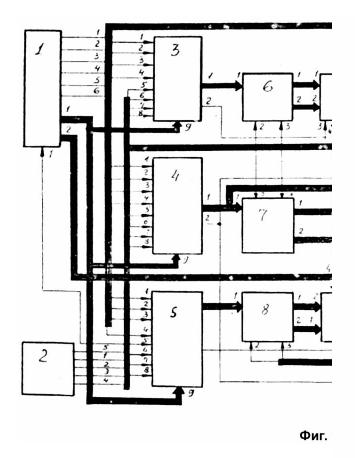

На фиг.1 представлена структурная схема устройства вычисления быстрых геометрических преобразований; на фиг.2 представлен вариант схемотехнической реализации блока преобразования координат; на фиг.3 - преобразователя логарифмического; на фиг.4 - функционального преобразователя; на фиг.5 - адресного формирователя; на фиг.6 - блока формирования линии бесконечно удаленных точек; на фиг.7 - блока управления.

Устройство (фиг.1) содержит: блок 1 задания входных параметров (БЗВП); блок управления 2; первый блок 3, второй блок 4, третий блок 5 преобразования координат (ВПК); первый 6, второй 7 и третий 8 преобразователи логарифмические (ПЛ) первый 9 и второй 10 функциональные преобразователи (ФП); первый 11 и второй 12 адресные формирователи (АФ); блок 13 формирования линии бесконечно удаленных точек (БФЛТ); блок 14 памяти (БП).

В блоке управления 2 синхрогенератор вырабатывает стандартные телевизионные сигналы и формирует: импульсы с частотой, задающей моменты формирования пикселов по строке (выход 1); строчные гасящие импульсы -СГИ (выход 2) и кадровые гасящие импульсы КГИ (выход 3).

Бпок задания входных параметров предназначен пересылки для информационным выходам 1 и 2) за время гашения кадра параметров, постоянных в пределах одного кадра: \$|| в первый блок 3, второй блок 4 и третий блок 5 преобразования координат, а также Хо, Zo и Руо в первый 11 и адресные второй 12 формирователи. Синхронизация пересылки осуществляется с помощью управляющих сигналов (управляющие входы 1 - 6).

В основу организации структуры устройства положен параллельно-конвейерный принцип. Три одинаковые ветви (блоки 3, 6; 4, 7 и 5, 8) параллельно ведут вычисление эквивалентных соотношений типа:

$S_{i1}X_9+S_{i2}Z_9+S_{i3}$ ,  $log_2(S_{i1}X_9+S_{i2}Z_9+S_{i3})$ . Две одинаковые ветви (блоки 9, 11 и 10, 12) параллельно ведут вычисления адресов блока памяти соответственно по формулам (7, 8). Каждая ветвь имеет конвейерную структуру, темп которой задается синхроимпульсами блока управления.

Работу устройства рассмотрим с момента появления на втором и третьем выходах синхрогенератора соответственно строчного и кадрового гасящего импульсов. При этом блок управления формирует импульсы соответственно "Сброс СГИ" и "Сброс КГИ", которые устанавливают устройство в исходное состояние, а также "Обмен", который инициирует передачу параметров из БЭВП, Каждый параметр, выставляемый БЭВП на информационных шинах 1 и 2, сопровождается парой управляющих сигналов по управляющим первый устанавливает по соответствующий регистр в режим "Прием", второй синхросигнал "Запись" поступает на синхровходы всех регистров, предназначенных для хранения параметров, обеспечивая их запись в регистры. После окончания действия импульса КГИ блок управления начинает выдавать на одном из своих выходов серию синхроимпульсов, управляющих вычислительным конвейером в

устройстве. Частота этих синхроимпульсов соответствует темпу прорисовки пикселов на экране телевизионного приемника. На каждый синхроимпульс на выходе блока появляется информация, соответствующая пикселу экрана. После отображения очередной строки синхрогенератор вырабатывает импульс СГИ. который инициирует выработку блоком управления сигнала "Сброс СГИ", который устанавливает узлы устройства в состояние, соответствующее началу строки, а затем формирование кадра заканчивается появлением на выходах 2 и 3 синхрогенератора соответственно СГИ и КГИ.

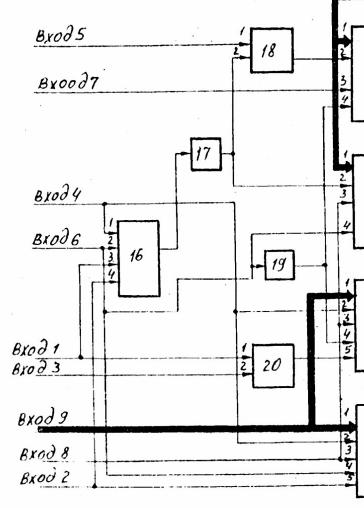

устройстве В предлагаемом преобразования координат содержит: комбинационный сумматор 25, первый 18 и второй 20 элементы ИЛИ, элемент НЕ 19, комбинационный узел 16, элемент задержки 17, а также первый 21, второй 22, третий 23 и четвертый 24 регистры. Входы 1, 2, 3 являются входами сигнала сопровождения первого, второго и третьего параметра направляющего косинуса; вход 4 входом разрешения записи; вход 5 - первым синхровходом; вход 6 - вторым синхровходом; вход 7 - первым входом сброса в ноль; вход 8 - вторым входом сброса в ноль; вход 9 - входом параметра направляющего косинуса.

Первый синхровход блока соединен с первым входом первого элемента ИЛИ, вход которого соединен с входом разрешения записи первого регистра, информационный вход которого соединен с информационным входом второго регистра и выходом комбинационного сумматора, первый информационный вход которого через монтажное ИЛИ соединен с выходами первого и второго регистров и информационным выходом блока, выходы третьего и четвертого регистров через монтажное ИЛИ соединены со вторым комбинационного информационным входом сумматора, вход кода параметра направляющей косинуса блока соединен с информационными входами третьего и четвертого регистров, входы разрешения записи которых соединены с одноименными входами блока и с первым входом комбинационного узла, первый вход сброса блока соединен с входом установки в ноль первого регистра, вход запрещения выходов которого соединен с одноименным входом третьего регистра и выходом элемента НЕ, вход которого соединен с входами запрещения выходов второго и четвертого регистров, вторым входом комбинационного узла и вторым синхровходом блока, вход сигнала сопровождения первого параметра направляющей косинуса которого соединен с третьим входом комбинационного узла и первым входом второго элемента ИЛИ, второй вход которого соединен с входом сигнала сопровождения третьего параметра направляющей косинуса блока, вход сопровождения второго параметра направляющей косинуса соединен с четвертым входом комбинационного узла и входом разрешения приема четвертого регистра, вход установки в ноль которого соединен с одноименными входами второго и третьего регистров и вторым входам сброса блока, выход комбинационного узла соединен с входом элемента задержки, выход которого соединен со вторым входом первого элемента ИЛИ и входом разрешения записи второго регистра, выход второго элемента ИЛИ соединен с входом

разрешения приема третьего регистра, выход знакового разряда блока соединен через монтажное ИЛИ с выходами старших разрядов первого и второго регистров.

ВПК предназначен для вычисления выражения  $S_{i1}X_3+S_{i2}Z_3+S_{i3}$ , содержащегося в дробях соотношений (1 и 2).

Комбинационная схема по входу реализует следующую функцию

## f=Bx.2VBx.1(Bx.3VBx.4).

Схема работает следующим образом. Первый и второй регистры установлены постоянно в режим "приема". При отсутствии сигнала на шестом входе первый и третий регистры находятся в режиме "разрешение выходов", а второй и четвертый - "запрещение выходов" (в третьем или Z состоянии). Работу ВПК рассмотрим с момента поступления на седьмой и восьмой входы импульсов соответственно "Сброс СГИ" и "Сброс КГИ", вырабатываемых блоком управления. Эти импульсы устанавливают все регистры ВПК в нулевое состояние и подготавливают ВПК к приему параметров из БЭВП. Первым на девятый вход поступает в параллельном коде значение коэффициента 513. затем на третий вход из БЭВП поступает сигнал сопровождения \$13. устанавливающий третий регистр по входу в режим "приема". После этого на четвертый вход из БЭВП поступает синхросигнал "запись", осуществляющий запись параметра 5і3 в третий регистр, а через комбинационный сумматор - в первый и второй регистры.

После записи параметра Si3 на девятый вход подается код параметра Si1 который запишется в третий регистр после подачи из БЭВП на первый вход сигнала сопровождения Si1 а на четвертый вход синхросигнала "Запись".

Последним в четвертый регистр передается параметр  $S_{12}$ , для этого БЭВП выставляет на девятый вход код  $S_{12}$ , затем - на второй вход сигнал сопровождения  $S_{12}$ , а на четвертый вход синхросигнал "Запись".

Далее из блока управления на пятый вход поступает серия из n синхроимпульсов C1 (где n число пикселов в строке). При поступлении 1-10 импульса в первый регистр записывается сумма JS11+S13. После поступления последнего импульса этой серии, т.е. после окончания прорисовки последнего пиксела в очередной 1-0й строке, на седьмой вход из блока управления поступает импульс "Сброс СГИ", обнуляющий первый регистр. Затем на шестой вход из блока управления поступает импульс С2, который переводит первый и третий регистры в состояние "запрещения выходов", а второй и четвертый -"разрешения выходов". Кроме этого, импульс С2 осуществляет запись в первый и второй регистры IS12+S13.

Теперь при поступлении на пятый вход J-го импульса из очередной серии из n синхроимпульсов в первом регистре будет формироваться сумма JSI1+ ISI2+SI3. Полный цикл работы ВПК завершится при достижении J=n, I=m, где m - число телевизионных строк в

кадре, и приходу импульсов "Сброс СГИ" и "Сброс КГИ", устанавливающих БПК в исходное состояние.

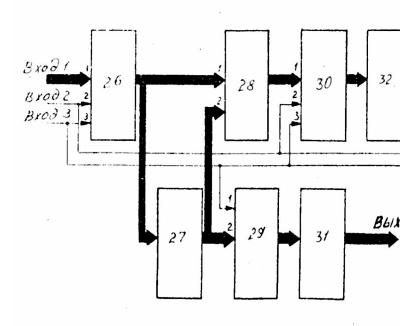

Преобразователь логарифмический содержит входной регистр 26, первый 30 и второй 33 промежуточные регистры, схему управления блоком сдвига аргумента 27 (СУБСА), блок сдвига аргумента 28 (БСА), элемент задержки 29, постоянное запоминающее устройство 32, блок элементов НЕ 31 и комбинационный сумматор 34, вход 1 является информационным входом, вход 2 синхровходом, вход 3 - вход сброса.

Информационный вход преобразователя соединен с информационным входом входного регистра, выход которого соединен информационным входом блока сдвига аргумента и входа блока управления сдвигом, выход которого соединен с информационным входом блока задержки и с входом блока управления сдвигом которого аргумента. выход соединен информационным входом первого промежуточного регистра, выход которого соединен с адресным входом блока памяти, выход которого соединен с информационным входом второго промежуточного регистра; выходы опорного значения функции логарифма и поправки которого соединены соответственно первым и вторым С информационными входами комбинационного сумматора, выход которого является первым выходом преобразователя, вторым выходом которого является выход блока элементов НЕ, вход которого соединен с выходом блока задержки, вход которого соединен с установки В ноль олноименными входами первого и второго промежуточного регистров, входного регистра и входом сброса преобразователя, синхровход которого соединен с синхровходами входного регистра и первого и второго промежуточных регистров.

ПЛ осуществляет аппаратную реализацию логарифма, финкции двоичного используется для вычисления (3, 4). ПЛ работает следующим образом. Сигналом "Сброс СГИ", поступающим из блока управления на третий вход, все регистры ПЛ устанавливаются в нулевое состояние. На первый вход из ВПК в параллельном коде поступает число, которое по импульсу серии С1 записывается во входной регистр. С выхода входного регистра это число поступает на БСА и на СУБСА. На выходе СУБСА (см. решение о выдаче авторского свидетельства от 19.12.89г. по заявке 4663108) формируется двоичный код управления БСА. Фактически, БСА и СУБСА формируют в первом промежуточном регистре число e<sub>m</sub> (5), Из соответствии CO значением осуществляется выборка опорного функции логарифма и ее поправки. Значения этих величин записывается во второй промежуточный регистр и суммируются в сумматоре, на выходе которого образуется значение 1092ем с требуемой точностью. Параллельно СУБСА и блок инверторов формируют de+  $\Delta$  d, где  $\Delta$  d=19. Элемент задержки обеспечивает одновременное появление информации на первом и втором выходах ПЛ.

Функциональный преобразователь содержит первый 35, второй 36, третий 38, четвертый 40 регистры, блок памяти 39, первый 37 и второй 41 комбинационные сумматоры, входы 1, 4 - это входы целой части первого и второго операндов; входы 2, 5 - входы дробной части первого и второго операндов; вход 3 - синхровход; вход 4 - вход

сброса.

Входы целой части первого и второго операндов преобразователя соединены с первым и третьим информационными входами первого комбинационного сумматора, второй и четвертый информационные входы которого соединены с выходами первого и второго регистров, информационные входы которых соединены с входами дробной части первого и второго операндов преобразователя, синхровход которого соединен с входами разрешения записи первого, второго, третьего и четвертого регистров, входы установки в ноль которых соединены с входом сброса преобразователя, выход дробной части первого комбинационного сумматора соединен с информационным входом третьего регистра, выход которого соединен с адресным входом блока памяти, выход которого соединен с информационным входом четвертого регистра, выходы функции и поправки которого соединены с первым и вторым информационными входами второго комбинационного сумматора, выход соединен с первым κοτοροιο выходом преобразователя, второй вход которого соединен с выходом целой части первого комбинационного сумматора.

Назначение ФП состоит в формировании на первом выходе значения функции  $2^{K}$  (6), а на втором выходе - d (6).

ФП работает следующим образом. Импульс "Сброс СГИ" (вход 6) устанавливает в нулевое состояние все регистры, на первый и четвертый поступают код целых соответственно log2a и log2b (6), а на второй и входы поступают дробные соответственно log2a и log2b (6). По импульсу С1, поступающему на третий вход ФП, дробные части логарифмов записываются в первый и второй регистры. На первом комбинационном сумматоре осуществляется вычисление разности Log2a-log2b. С его первого выхода код d целой части разности поступает на первый выход ФП, а со второго выхода - код К дробной части разности. По импульсу С1 код К записывается в третий регистр и с его выхода поступает на ПЗУ. По значению К из ПЗУ извлекается значение функции  $2^{K}$ , где -1 < K < 1, с соответствующей поправкой и по очередному импульсу С1 записывается в четвертый регистр. На втором комбинационном сумматоре осуществляется соответствующих суммирование значений функции и поправки.

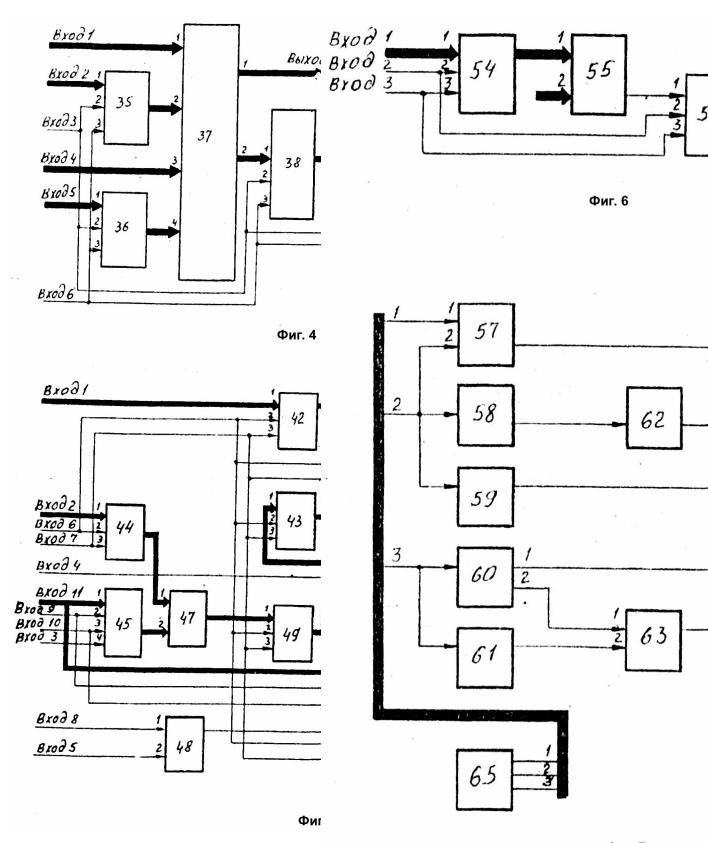

Адресный формирователь содержит первый 42, второй 43, третий 44, четвертый 45, пятый 49, шестой 51 и седьмой 52 регистры, блок сдвига 46, узел формирования знака 48, узел задержки 50, первый 47 и второй 53 комбинационные сумматоры, входы 1, 2 являются входами первого и второго операнда соответственно; входы 3, 4 входами сигналов сопровождения кода порядка и кода мантиссы; входы 5, 8 входами знака первого и второго операнда соответственно; вход 6 входом синхронизации; сходы 7, 10 первым и вторым входом сброса соответственно; вход 9 входом разрешения записи.

Вход первого операнда формирователя соединен с информационным входом первого

регистра, выход которого соелинен информационным входом блока сдвига, а вход управления сдвигом которого соединен с выходом второго регистра, выходы третьего и четвертого регистров соединены с первым и вторым информационными входами первого комбинационного сумматора, выход которого соединен с информационным входом пятого регистра, выход которого соединен информационным входом второго регистра, вход разрешения записи которого ∞единен одноименными входами узла задержки первого, шестого, пятого и третьего регистров и входом синхронизации формирователя, первый вход сброса которого соединен с входами установки в ноль первого, второго, третьего, пятого и шестого регистров и узла задержки, информационный вход которого соединен с выходом узла формирования знака, первый и второй входы которого соединены с входами знаков первого и второго операндов формирователя, вход второго операнда которого соединен с информационным входом третьего регистра, вход кода параметра и мантиссы формирователя соединен с информационными входами четвертого и седьмого регистров, входы разрешения записи которых соединены с входом разрешения записи формирователя, второй вход сброса которого соединен с входами установки в ноль четвертого и седьмого регистров, входы сигналов сопровождения кода порядка и кода мантиссы преобразователя соединены с входами разрешения приема четвертого и седьмого регистров соответственно, выход блока сдвига соединен с информационным входом шестого регистра, выходы шестого и седьмого регистров соединены с первым и вторым информационными входами второго комбинационного сумматора, третий информационный вход которого соединен с узла задержки, выход выхолом второго комбинационного сумматора является выходом преобразователя.

АФ предназначен для вычисления координат проекции элемента экрана на предметную плоскость по формуле (7) или (8).

АФ функционирует следующим образом. За время гашения кадра БЗВП осуществляет пересылку в АФ по одиннадцатому входу параметров Руо и Хо (Zо - для второго АФ). Первым на одиннадцатый вход в параллельном коде поступает значение Руо - Затем на третий вход из БЗВП поступает сигнал сопровождения Руо устанавливающий четвертый регистр по входу в режим "Приема". После этого на вход 9 из БЗВП поступает синхросигнал "Запись", осуществляющий запись параметра  $^{P_{y_0}}$  в регистр. После записи параметра Руо поступает код параметра Хо. который запишется в седьмой регистр аналогичным образом. В течение времени формирования кадра АФ реализует следующие действия.

На втором входе АФ устанавливается код  $d_x$  (7), поступающий из ФП. Импульсом C1 он запишется в третий регистр. На первом сумматоре выполнится  $d_x$ +  $P_{yo}$ , этот результат по импульсу C1 запишется в пятый регистр. В этот момент на первом входе АФ установится код  $2^{K_x}$ , который запишется в первый регистр очередным импульсом

С1. одновременно по этому же сигналу информация из пятого регистра перепишется во второй. Схема сдвига реализуется на г мультиплексоре. Первый вход этой схемы является информационным входом, а второй вход - адресным входом мультиплексора. Схема сдвига реализует функцию результат запишется в шестой регистр по импульсу С1.

Знак выражения  $2^{K_X}$   $2^{d_X}$   $+ P_{Yo}$  формируется схемой формирования знака, которая реализована по схеме сумматора по **mod2**. Схема задержки, выполненная на регистре сдвига, обеспечивает одновременную подачу информации по первому и третьему входам второго комбинационного сумматора. На выходе которого формируется окончательный результат.

Блок формирования линии бесконечно удаленных точек (БФЛТ) содержит входной регистр 54, дешифратор нуля 53, узел задержки 56, вход 1 является информационным входом; вход 2 - входом синхронизации; вход 3 - входом сброса.

Выход узла задержки является выходом блока, информационный вход которого соединен с информационным входом входного регистра, выход которого соединен с входом дешифратора нуля, выход которого соединен с информационным входом узла задержки, вход разрешения записи которого соединен с одноименным входом входного регистра и входом синхронизации блока, вход сброса которого соединен с входом установки в ноль входного регистра и узла задержки.

БФЛТ предназначен для формирования на телевизионного приемника горизонта и функционирует следующим образом. На третий вход блока и одновременно на третий вход входного регистра и узла задержки, выполненном на сдвигающем регистре, поступает из блока управления импульс "СБРОС СГИ", который устанавливает регистры в исходное состояние. На первый вход блока и на одноименный вход входного регистра поступает параллельный код знаменателя дробной части выражений (1 и 2). По импульсу C1, поступающему на второй вход блока и одновременно на второй вход входного регистра, осуществляется запись кода во входной регистр. Выход регистра подключен к первому входу дешифратора нуля, а на второй его вход подается код нуля. В случае равенства знаменателя выражений (1 и 2) нулю на выходе дешифратора нуля устанавливается сигнал, соответствующий задержки обеспечивает единице. Узеп одновременное появление связанной во времени информации с выходов БФЛТ и блока памяти.

Блок управления содержит узел синхронизации 65, триггер 57, первый 58, второй 61 элементы задержки, первый 59, второй 60, третий 62 узлы формирования импульсов и элемент И 63, первый выход узла синхронизации соединен с тактовым входом триггера, выход которого является первым выходом блока, второй выход узла синхронизации соединен с входом установки в ноль триггера, с входами первых элементов, задержки и узла формирования импульсов, третий вход узла синхронизации

соединен с входами вторых узла формирования импульсов и элемента задержки, выход первого элемента задержки соединен с входом третьего узла формирования импульсов, выход которого является вторым выходом блока, третьим выходом является которого выход первого формирования импульсов, первый выход второго узла формирования импульсов соединен с четвертым выходом блока, пятый выход которого соединен с выходом элемента И, первый и второй входы которого соединены со вторым выходом второго узла формирования импульсов и второго элемента задержки соответственно.

Блок управления предназначен для синхронизации функционирования всего, устройства: инициирует передачу входных параметров БЗВП, когда появляется кадровый гасящий импульс, и вырабатывает серию синхроимпульсов С1 управляющих конвейером в течение времени формирования кадра.

управления работает следующим образом. Из первый вход триггера, работающего в режиме деления частоты, поступают из синхрогенератора импульсы, задающие моменты формирования пикселов на строке. На выходе триггера формируются синхроимпульсы С1. На второй вход установки в ноль триггера, на первый элемент задержки и на первый формирователь поступает из синхрогенератора серия СГИ. На каждый импульс СГИ блокируется формирование триггером серии С1, первым формирователем формируется импульс "Сброс СГИ", а цепочка первый элемент задержки - третий формирователь формирует импульс С2, задержанный отношению к соответствующему импульсу "Сброс СГИ" на время установки регистра в ноль. Частота серии импульсов C2 в n раз меньше, где n - число пикселов в строке, частоты серии С1. На входы второго формирователя и второго элемента задержки поступают из синхрогенератора кадровые гасящие импульсы КГИ. На каждый импульс КГИ на выходе. второго формирователя формируется импульс "Сброс КГИ", а второй формирователь, второй элемент задержки и элемент И формируют импульс "Обмен", передний фронт которого задержан по отношению к соответствующему импульсу "Сброс КГИ" на время установки в ноль регистра.

Фиг. 3

Фиг. 2

Фиг. 7