# KHARKOV NATIONAL UNIVERSITY OF RADIOELECTRONICS

# Proceedings of IEEE East-West Design & Test Symposium (EWDTS'2011)

Copyright © 2011 by the Institute of Electrical and Electronics Engineers, Inc.

Technically Co-Sponsored by

Sevastopol, Ukraine, September 9 – 12, 2011

# IEEE EAST-WEST DESIGN AND TEST SYMPOSIUM 2011 ORGANISING COMMITTEE

## **General Chairs**

V. Hahanov – Ukraine

Y. Zorian - USA

### **General Vice-Chairs**

R. Ubar – Estonia

E. Pashkov – Ukraine

P. Prinetto - Italy

# **Program Chairs**

S. Shoukourian - Armenia

D. Speranskiy – Russia

# **Program Vice-Chairs**

M. Renovell – France

Z. Navabi – Iran

# **Steering Committee**

M. Bondarenko – Ukraine

V. Hahanov - Ukraine

R. Ubar - Estonia

Y. Zorian - USA

# **Publicity Chairs**

G. Markosyan - Armenia

S. Mosin - Russia

# **Public Relation Chair**

V. Djigan - Russia

# **Program Committee**

E. J. Aas - Norway

J. Abraham - USA

M. Adamski - Poland

A . Barkalov – Poland

R. Bazylevych - Ukraine

A. Chaterjee - USA

V. Djigan – Russia

A. Drozd - Ukraine

E. Evdokimov - Ukraine

E. Gramatova - Slovakia

A. Ivanov – Canada

M. Karavay - Russia

V. Kharchenko – Ukraine

K. Kuchukjan - Armenia

W. Kuzmicz - Poland

A. Matrosova - Russia

V. Melikyan – Armenia

L. Miklea – Romania

O. Novak - Czech Republic

Z. Peng – Sweden

A. Petrenko - Ukraine

D. Puzankov - Russia

J. Raik - Estonia

A. Romankevich - Ukraine

A. Ryjov – Russia

R. Seinauskas - Lithuania

S. Sharshunov - Russia

A. Singh - USA

J. Skobtsov - Ukraine

V. Tverdokhlebov -- Russia

V. Vardanian – Armenia

V. Yarmolik - Byelorussia

# **Organizing Committee**

Yu. Gimpilevich – Ukraine

S. Chumachenko – Ukraine

E. Litvinova – Ukraine

# **EWDTS 2011 CONTACT INFORMATION**

Prof. Vladimir Hahanov Design Automation Department Kharkov National University of Radio Electronics, 14 Lenin ave, Kharkov, 61166, Ukraine.

Tel.: +380 (57)-702-13-26

E-mail: hahanov@kture.kharkov.ua Web: www.ewdtest.com/conf/

# 9th IEEE EAST-WEST DESIGN & TEST SYMPOSIUM (EWDTS 2011)

Sevastopol, Ukraine, September 9-12, 2011

The main target of the IEEE East-West Design & Test Symposium (EWDTS) is to exchange experiences in the field of design, design automation and test of electronic circuits and systems, between the technologists and scientists from Eastern and Western Europe, as well as North America and other parts of the world. The symposium aims at attracting attendees especially from the Newly Independent States (NIS) and countries around the Black Sea and Central Asia.

We cordially invite you to participate and submit your contribution(s) to EWDTS'11 which covers (but is not limited to) the following topics:

- · Analog, Mixed-Signal and RF Test

- Analysis and Optimization

- ATPG and High-Level TPG

- Built-In Self Test

- Debug and Diagnosis

- Defect/Fault Tolerance and Reliability

- Design for Testability

- Design Verification and Validation

- EDA Tools for Design and Test

- Embedded Software Performance

- Failure Analysis, Defect and Fault

- FPGA Test

- HDL in test and test languages

- High-level Synthesis

- High-Performance Networks and Systems on a Chip

- Low-power Design

- Memory and Processor Test

- Modeling & Fault Simulation

- Network-on-Chip Design & Test

- Modeling and Synthesis of Embedded Systems

- Object-Oriented System Specification and Design

- On-Line Test

- Power Issues in Testing

- Real Time Embedded Systems

- Reliability of Digital Systems

- Scan-Based Techniques

- Self-Repair and Reconfigurable Architectures

- Signal and Information Processing in Radio and Communication Engineering

- System Level Modeling, Simulation & Test Generation

- Using UML for Embedded System Specification

### **CAD Session**:

- CAD and EDA Tools, Methods and Algorithms

- Design and Process Engineering

- Logic, Schematic and System Synthesis

- Place and Route

- Thermal, Timing and Electrostatic Analysis of SoCs and Systems on Board

- Wireless Systems Synthesis

- Digital Satellite Television

The EWDTS'2011 will take place in Sevastopol, Ukraine. Sevastopol is a port city, located on the Black Sea coast of the Crimea peninsula. The city, formerly the home of the Soviet Black Sea Fleet, is now home to a Ukrainian naval base and facilities leased by the Russian Navy and used as the headquarters of both the Ukrainian Naval Forces and Russia's Black Sea Fleet.

The symposium is organized by Kharkov National University of Radio Electronics in cooperation with Sevastopol National Technical University and Tallinn University of Technology. It is technically cosponsored by the IEEE Computer Society Test Technology Technical Council (TTTC) and financially supported by Virage Logic, Synopsys, Aldec, Kaspersky Lab, DataArt Lab, Tallinn Technical University, Cadence.

# CONTENTS

| Taavi Viilukas, Maksim Jenihhin, Jaan Raik, Raimund Ubar, Samary Baranov                                                                                             | . 13 |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| About Dependability in Cyber-Physical Systems Liviu Miclea, Teodora Sanislav                                                                                         | . 17 |

| Self-healing Capabilities through Wireless Reconfiguration of FPGAs  George Dan Moiş, Mihai Hulea, Silviu Folea and Liviu Miclea                                     | . 22 |

| Software Testing of a Simple Network  Jack H. Arabian                                                                                                                | . 28 |

| A New Core to Monitor RTOS Activity in Embedded Systems  Dhiego Silva, Letícia Bolzani, Fabian Vargas                                                                | . 32 |

| A unifying formalism to support automated synthesis of SBSTs for embedded caches  Stefano Di Carlo, Giulio Gambardella, Marco Indaco, Daniele Rolfo, Paolo Prinetto  | . 39 |

| Simulation-Based Hardware Verification with Time-Abstract Models  Alexander Kamkin                                                                                   | . 43 |

| Programmable Current Biasing for Low Noise Voltage Controlled Oscillators  Vazgen Melikyan, Armen Durgaryan                                                          | . 47 |

| Adaptive Signal Processing in Multi-Beam Arrays Victor I. Djigan                                                                                                     | . 51 |

| Optimization of Microprogram Control Unit with Code Sharing  A. Barkalov, L.Titarenko, L.Smolinski                                                                   | . 55 |

| Synthesis of control unit with refined state encoding for CPLD devices  A.Barkalov, L.Titarenko, S.Chmielewski                                                       | . 60 |

| Cybercomputer for Information Space Analysis<br>Vladimir Hahanov, Wajeb Gharibi, Dong Won Park, Eugenia Litvinova                                                    | . 66 |

| Verification and Diagnosis of SoC HDL-code Vladimir Hahanov, Dong Won Park, Olesya Guz, Sergey Galagan, Aleksey Priymak                                              |      |

| Diagnosis Infrastructure of Software-Hardware Systems Tiecoura Yves, Vladimir Hahanov, Omar Alnahhal, Mikhail Maksimov, Dmitry Shcherbin, Dmitry Yudin               | . 84 |

| Overview of the Prototyping Technologies for Actel® RTAX-S FPGAs  Olga Melnikova                                                                                     | . 90 |

| Hardware Reduction for Matrix Circuit of Control Moore Automaton  A. Barkalov, L.Titarenko, O. Hebda                                                                 | . 94 |

| RoCoCo: Row and Column Compression for High-Performance Multiplication on FPGAs  Fatih Ugurdag, Okan Keskin, Cihan Tunc, Fatih Temizkan, Gurbey Fici, Soner Dedeoglu | . 98 |

| Test Architecture Design for TSV based 3D Stacked ICs using Hard SOCs  Surajit K. Roy, Chandan Giri, Arnab Chakraborty, Subhro Mukherjee,  Debesh K. Das and Hafizur Rahaman                        | . 102 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| Efficient selective compaction and un-compaction of inconsequential logical design units in the schematic representation of a design  Tarun Kumar Goyal, Amarpal Singh, Rahul Aggarwal              | . 106 |

| Quasioptimal Algorithm of Carrier Recovery in Coherent Receiver of M-ary Alphabets APK-Signals without Traditional PLL  Victor V. Panteleev                                                         | . 112 |

| Quasioptimal Algorithm of Timing Recovery in Autocorrelation Receiver of Phase Shift Keying Signal Vitaliy A. Balashov, Victor V. Panteleev, Leonid M. Lyakhovetskyy                                |       |

| Design of Microprogrammed Controllers with Address Converter implemented on Programmable Systems with Embedded Memories Remigiusz Wiśniewski, Monika Wiśniewska, Marek Węgrzyn, Norian Marranghello | . 123 |

| Reduction of the Memory Size in the Microprogrammed Controllers  Monika Wiśniewska, Remigiusz Wiśniewski, Marek Węgrzyn, Norian Marranghello                                                        | . 127 |

| Maintaining Uniformity in the Processes of Encryption and Decryption with a Variable Number of Encryption Rounds  L. Smolinski                                                                      | . 131 |

| C++TESK-SystemVerilog United Approach to Simulation-Based Verification of Hardware Designs  Mikhail Chupilko                                                                                        | . 136 |

| Advanced Scan Chain Configuration Method for Broadcast Decompressor Architecture  Jiří Jeníček and Ondřej Novák, Martin Chloupek                                                                    | . 140 |

| A Programmable BIST with Macro and Micro codes for Embedded SRAMs  P. Manikandan, Bjørn B Larsen, Einar J Aas, Mohammad Areef                                                                       | . 144 |

| Modified Protocol for Data Transmission in Ad-Hoc Networks with High<br>Speed Objects Using Directional Antennas<br>Victor Barinov, Alexey Smirnov, Danila Migalin                                  | . 150 |

| High Performance Audio Processing SoC Platform  Denis Muratov, Vladimir Boykov, Yuri Iskiv, Igor Smirnov, Sergey Berdyshev, Valeriy Vertegel, Yuri Gimpilevich, Gilad Keren                         |       |

| Methodology of the Pre-silicon Verification of the Processor Core Sergii Berdyshev, Vladimir Boykov, Yuri Gimpilevich, Yuri Iskiv, Gilad Keren, Denis Muratov, Igor Smirnov, Valeriy Vertegel       | . 158 |

| Spam Diagnosis Infrastructure for Individual Cyberspace<br>Vladimir Hahanov, Aleksandr Mischenko, Svetlana Chumachenko, Anna Hahanova,<br>Alexey Priymak                                            | . 161 |

| A Security Model of Individual Cyberspace  Alexander Adamov, Vladimir Hahanov                                                                                                                       | . 169 |

| Organization of Pipeline Operations in Mapping Unit of the Dataflow Parallel Computing System  Levchenko N.N., Okunev A.S, Yakhontov D.E                                                                           | 173 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| A Subsystem for Automated Synthesis of LFSR-Based Test Generator for Deterministic and Pseudorandom Testing Sergey G. Mosin, Natalia V. Chebykina, Maria S. Serina                                                 | 177 |

| Debugging and testing features of the dataflow parallel computing system components and devices                                                                                                                    | ,,  |

| Levchenko N.N., Okunev A.S., Yakhontov D.E., Zmejev D.N.                                                                                                                                                           | 180 |

| Adaptive Wavelet Codec for Noisy Image Compression  Yuri S. Bekhtin                                                                                                                                                | 184 |

| TCAD-SPICE simulation of MOSFET switch delay time for different CMOS technologies K. O. Petrosyants, E. V. Orekhov, D. A. Popov, I. A. Kharitonov, L. M. Sambursky, A. P. Yatmanov, A. V. Voevodin, A. N. Mansurov | 188 |

| Design Fault Injection-Based Technique and Tool for FPGA Projects Verification  L. Reva , V. Kulanov, V. Kharchenko                                                                                                | 191 |

| Optimal Schematic Design of Low-Q IP Blocks Sergey G. Krutchinsky, Mikhail S. Tsybin                                                                                                                               | 196 |

| Parallelizing of Boolean function system for device simulation  Alexander Chemeris, Svetlana Reznikova                                                                                                             | 200 |

| Optimization Some Characteristics of Continuous Phase Spread Spectrum Signal  Michael Balanov, Olga Mamedova                                                                                                       | 203 |

| Development Methodology of Interoperable Add-on Tool for Static Verification of Current Density  E. Babayan                                                                                                        | 207 |

| Design Consideration of CMOS Low Cut-Off Low Pass Filter for ECG Applications  Andranik Hovhannisyan                                                                                                               | 210 |

| Method of Capacitor Calibration for Switched Capacitor Circuits  Norayr K. Aslanyan                                                                                                                                | 214 |

| Built-in Measurement Technique for On-Chip Capacitors<br>Andranik S Hovhannisyan, Norayr K Aslanyan, Vahram K Aharonyan, Hayk H Dingchyan                                                                          | 217 |

| A Generation of Canonical Forms for Design of IIR Digital Filters<br>Vladislav A. Lesnikov, Alexander V. Chastikov, Tatiana V. Naumovich, Sergey V. Armishev                                                       | 221 |

| Variant of Wireless MIMO Channel Security Estimation Model Based on Cluster Approach  O. Kuznietsov, O. Tsopa                                                                                                      | 225 |

| Compact DSM MOSFET Model and its Parameters Extraction  Anatoly Belous, Vladislav Nelayev, Sergey Shvedov, Viktor Stempitsky,  Tran Tuan Trung, Arkady Turtsevich                                                  | 230 |

| IGBT Technology Design and Device Optimization  Artem Artamonov, Vladislav Nelayev, Ibrahim Shelibak, Arkady Turtsevich                                                                                            | 233 |

| Device-Process Simulation of Discrete Silicon Stabilitron with the Stabilizing Voltage of 6,5 V <b>Dudar N.L., Borzdov V.M.</b>                                                                 | . 237 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| Geometrical Approach to Technical Diagnosing of Automatons  Tverdokhlebov V.A.                                                                                                                  | . 240 |

| Loop Fusion and Power Consumption of PCs  Dmytro Lazorenko                                                                                                                                      | . 244 |

| On Experimental Research of Efficiency of Tests Construction for Combinational Circuits by the Focused Search Method Vasily Kulikov, Vladimir Mokhor                                            | . 247 |

| Test Set Compaction Procedure for Combinational Circuits Based On Decomposition Tree  Valentina Andreeva                                                                                        | . 251 |

| Implementation by the Special Formula of an Arbitrary Subset of Code Words of $(m, n)$ -code for Designing a Self-Testing Checker  N. Butorina, S. Ostanin                                      | . 255 |

| Optimal Fluctuations for Satisfactory Performance under Parameter Uncertainty  HJ Kadim                                                                                                         | . 259 |

| The Evidential Independent Verification of Software of Information and Control Systems, Critical to Safety: Functional Model of Scenario  Konorev Borys, Sergiyenko Volodymyr, Chertkov Georgiy | . 263 |

| Si BJT and SiGe HBT Performance Modeling after Neutron Radiation Exposure  Konstantin Petrosyants, Eric Vologdin, Dmitry Smirnov, Rostislav Torgovnikov,  Maxim Kozhukhov                       | . 267 |

| Compact Power BJT and MOSFET Models Parameter Extraction with Account for Thermal Effects  I. A. Kharitonov                                                                                     | . 271 |

| Thermal Analysis of the Ball Grid Array Packages  K.O. Petrosyants, N.I. Rjabov                                                                                                                 | . 275 |

| On Synthesis of Degradation Aware Circuits at Higher Level of Abstraction  Mohammad Abdul Razzaq, Alok Baluni, Virendra Singh,  Ram Rakesh Jangiry and Masahiro Fujitaz                         | . 279 |

| Selection of the State Variables for Partial Enhanced Scan Techniques  A. Matrosova, A. Melnikov, R. Mukhamedov, V. Singh                                                                       | . 285 |

| Efficient Regular Expression Pattern Matching using Cascaded Automata Architecture for Network Intrusion Detection Systems  Pawan Kumar and Virendra Singh                                      | . 290 |

| Dispersion Analysis in Processes of Passive Monitoring and Diagnosing of Enterprise Area Networks  Anna V. Babich, Murad Ali A                                                                  | . 295 |

| A Diagnostic Model for Detecting Functional Violation in HDL-Code of System-on-Chip  Ngene Christopher Umerah, Vladimir Hahanov                                                                 | . 299 |

| Krivoulya G., Shkil A., Kucherenko D3                                                                                                                                          | 303 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| A Model of Spatial Thinking for Computational Intelligence  Kirill A. Sorudeykin                                                                                               | 311 |

| New Methods and Tools for Design of Tests Memory  Mudar Almadi, Diaa Moamar, Vladimir Ryabtsev3                                                                                | 319 |

| Scalability of "Ideal" System Networks Based on Quasy-Complete Graph Architecture  Mikhail F. Karavay and Victor S. Podlazov3                                                  | 326 |

| The Test Method for Identification of Radiofrequency Wireless Communication Channels Using Volterra<br>Model<br>Vitaliy D. Pavlenko, Viktor O. Speranskyy, Vladimir I. Lomovoy |     |

| A Calculation of Parasitic Signal Components Digital Filtration for the Retransmission Meter on the basi<br>of FPGA<br>Velichko D.A., Vdovychenko I.I                          |     |

| The Testware CAD Victor Zviagin3                                                                                                                                               | 337 |

| The Synthesis of Periodic Sequences with Given Correlation Properties  V. M. Koshevyy, D. O. Dolzhenko                                                                         | 341 |

| Lyapunov Function Analysis for Different Strategies of Circuit Optimization  A. Zemliak, A. Michua, T. Markina                                                                 | 345 |

| State Identification of Bilinear Digital System  Dmitriy Speranskiy                                                                                                            | 349 |

| Model order reduction of Micro-Electro-Mechanical Systems Petrenko Anatoly                                                                                                     | 355 |

| Modeling a Logical Network of Relations of Semantic Items in Superphrasal Unities  Nina Khairova, Natalia Sharonova                                                            | 360 |

| Resistance Dependent Delay Behavior of Resistive Open Faultsin Multi Voltage Designs Environment Mohamed Tag Elsir Mohammadat, Noohul Basheer Zain Ali, Fawnizu Azmadi Hussin  | 366 |

| Designing ISA Card with Easy Interface Taghi Mohamadi                                                                                                                          | 372 |

| Real Time Operating System for AVR Microcontrollers  Taghi Mohamadi                                                                                                            | 376 |

| Recognition of Automatons by their Geometrical Images  Epifanov A.S                                                                                                            | 381 |

| Problems of Cause-Effect Link's Definition in Man-Machine Systems' Accidents                                                                                                   | 385 |

| OFDM-based Audio Watermarking for Covered Data Transmission in VHF Radiotelephony  Oleksandr V. Shishkin, Oleksandr O. Lyashko                         | 389 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Validation&Verification of an EDA Automated Synthesis Tool Giulio Gambardella, Marco Indaco, Paolo Prinetto, Daniele Rolfo                             | 393 |

| Infrastructure for Testing and Diagnosing Multimedia Device Vladimir Hahanov, Karyna Mostova, Oleksandr Paschenko                                      | 394 |

| Architecture for an Intelligent Test Error Detection Agent  Matthias Kirmse, Uwe Petersohn, Elief Paffrath                                             | 400 |

| Cadence EDA Flow for IC's and Electronics  Anatoli Ivanov                                                                                              | 405 |

| Designing an Embedded System for Interfacing with Networks Based on ARM  Taghi Mohamadi                                                                | 407 |

| Checkability of the Digital Components in Safety-Critical Systems: Problems and Solutions  A. Drozd, V. Kharchenko, S. Antoshchuk, J. Sulima, M. Drozd | 411 |

| AUTHORS INDEX                                                                                                                                          | 416 |

# Spam Diagnosis Infrastructure for Individual Cyberspace

Vladimir Hahanov<sup>1</sup>, Aleksandr Mischenko<sup>2</sup>, Svetlana Chumachenko<sup>3</sup>,

Anna Hahanova, Alexey Priymak *Kharkov National University of Radioelectronics, Ukraine, 61166, Kharkov, Lenin Ave, 14,*E-mail: <sup>1</sup>hahanov@kture.kharkov.ua, <sup>2</sup>alex@simplesolutions.com.ua, <sup>3</sup>ri@kture.kharkov.ua

# **Abstract**

The theory, methods and the architecture of parallel information's analysis is presented by the form of analytical, graph and table forms of associative relations for the search, recognition, diagnosis of destructive components and the decision making in ndimensional vector cybernetic individual space. Vector -logical processes-models of actual oriented tasks are considered. They include the diagnostic of spam and the recovery of serviceability, the hardwaresoftware components of computer systems and the decision quality is estimated by the interactions of nonarithmetic metrics of Boolean vectors. The concept of self-development information of computer ecosystem is offered. It repeats the evolution of the functionality of the person. Original processes-models of associativelogical information analysis are represented on the basis of high-speed multiprocessor in n-dimensional vector discrete space.

# 1. Introduction

The problem of creating an effective infrastructure of cyberspace (Cyber Space), as well as self-developing information and computing ecosystems (ICES) of the planet is particularly important for global companies, such as Kaspersky Laboratory, Google and Microsoft.

Cyberspace as an object of nature is also susceptible to destructive components affecting the performance of subjects, which are computers, systems and networks. Therefore, now and in the future it remains as an important problem of space standardization and specialization of all the interacting entities, including the negative, as an integral part of the ecosystem. This action is permanent in time, whose purpose is to keep up, but one step ahead of the emergence of new malicious components, by creating an infrastructure cybernetic space, operating the computer ecosystem of the planet and the quality of each person's life.

Among the modules of such an infrastructure we can provide diagnosis of failures, and spam by

analyzing the information obtained at the testing stage and using of special methods of built-in search spam, standard-based boundary scan or assertion redundancy focused on spam detection, it will allow to identify and to eliminate spam without the use of external funds. So, it will be possible to do it without difficult exterior programs of modeling, testing and diagnosing by grafting of each e-mail testability intellectual redundancy package at the stage of its creation. It should use the predicate of recognition, which operates not only Boolean but register and matrix variables, making it nearly significant in formal writing the equations of diagnosis or recognition:

$$\begin{split} x^{a} &\approx x \oplus a = 0 \vee \underset{i}{\text{min}} \, Q_{i} \longrightarrow x \oplus a \oplus Q = 0; \\ x^{m} &\approx x \oplus m = 0 \vee \underset{i}{\text{min}} \, Q_{i} \longrightarrow x \oplus m \oplus Q = 0; \\ T \oplus S &= Q \approx \\ &\approx \begin{bmatrix} 00 & 1 & 1 & 1 \\ 01 & 1 & 1 & 1 \\ 11 & 1 & 1 & 1 \end{bmatrix} \Delta \begin{bmatrix} 1 & 1 & 1 \\ 1 & 1 & 1 \\ 1 & 1 & 1 \end{bmatrix} = \begin{bmatrix} 1 & 1 & 1 \\ 1 & 1 & 1 \\ 1 & 1 & 1 \end{bmatrix}$$

where  $x^a$ ,  $x^m$  - Predicate variables, a, m - values of variables,  $Q_i$  - an estimation of a cognizance of variable value; T - the test, S - the object which is subject to testing (program).

On the basis of recognition of the predicate mimage of any complexity, nature and shape can be created quite compact equation predicates forming intellectual solutions in the field of pattern recognition, decision making, testing, knowledge and technical facilities, diagnosis (recognition) among the spam emails.

In this regard, the proposed infrastructure of cyberspace, the metric to measure and model the process of analysis and synthesis of subjects give the opportunity to create effective solutions for computer products focused on Quick Search, detection and diagnosis not only positive but also negative subjects. Specifically, the proposed infrastructure can solve the

problem: 1) Description of the variety of cyberspace e-waste. 2) The formalization of the interaction of triad components <the program, spam, tests>. 3) Diagnosing and e-mail filtration. 4) The creation and effective utilization of spam basis. 5) The creation of high-speed intellectual means of self-developing service and protection of cyberspace.

It laid the basic principles of evolution, expressed even in the modern computer industry: 1) The standardization is the most important thing for evolution and life cycle ICS. The market doesn't accept and doesn't understand non-standard decisions on the interface. 2) Specialization is the efficiency provided by (personally oriented) services, products related to performance, quality, cost, energy saving by optimizing the structure and functional components that cover the specification. 3) Widespread use of vector-logical criteria of quality solutions to the problems of generating ideas, analysis and synthesis. Generation is a process of new functionality creation. In this synthesis it operates with existing components in the information space to create a structure. The analysis is an estimation of the received decision. 4) Hasse diagram is used to develop strategies to optimize coverage of the functional specification of library components or combinations, belonging to the information space. It is consistent with the modern Y-Technology, part of the ESL Design, which uses library components for all levels of product design to meet the Specified functionality in the synthesis process.

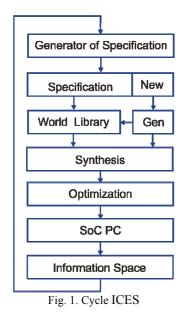

Fig. 1 is a vicious cycle of evolution ICES, which is actually isomorphic to the spiral of human development, wound on the time axis.

The purpose of this paper is the significant improvement of the quality of individual cyberspace

(ICP) of the user and cost reduction in operating costs due to vaccination ICP by adding a space infrastructure service, which includes libraries of positive and negative messages and provides testing, diagnosis and removal of harmful components of e-mails.

The object of study is a personal cyberspace with the information provided, its carriers and converters, as well as destructive components harmful to the functionality and improves the quality of human life.

Subject of research is the infrastructure service, which includes libraries of positive and negative messages and embedded software redundancy, which operates in real time, provides testing, diagnosis and removal of malicious and "junk" e-mail information, as described in the relevant libraries.

Motivation:

- 1) Lack of market AntiSpam protection built-in testing, diagnosing and removing harmful components that make up the infrastructure service, just as in digital systems in crystals, there are boundary-scan standards, and software products assertion redundancy focused on integrated testing of defects and errors, followed by a hardware or software products.

- 2) The theoretical development related to technology of algebraic vector analysis of information data-oriented high-performance solutions and estimation problems of recognition and images, action and testing facilities.

- 3) The presence of a model of production and marketing infrastructure of Kaspersky Lab is able to support the project of electronic communication technology vaccination and authority to offer to the market the information technologies.

- 4) Miniaturization and digital communications systems (phones, smart phones, tablets) require constant protection from the massive and unnecessary e-mails through the introduction of built-AntiSpam means controlling the exchange of information.

Tasks: 1) To develop mathematical tools of analysis of cyberspace based on the creation of models and methods of service of software products for testing, diagnosing and eliminating the massive unnecessary emails. 2) To create a standard process models and criteria for the interaction of e-mails with content analysis of useful functionality. 3) To develop the technology for analyzing the structure of the program code for determining the critical points and install the assertion operator monitors and manage the process of its functioning. 4) To create the infrastructure service functional programs for the embedded test, diagnosis and removal of harmful components of the software package of functionality through the use of library spam information. 5) To test and to verify integrated infrastructure service functionality that protects against malicious software code components.

# 2. Evolution of Cyber Space and Internet

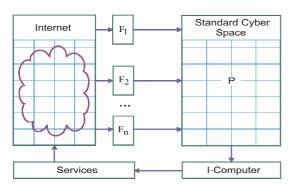

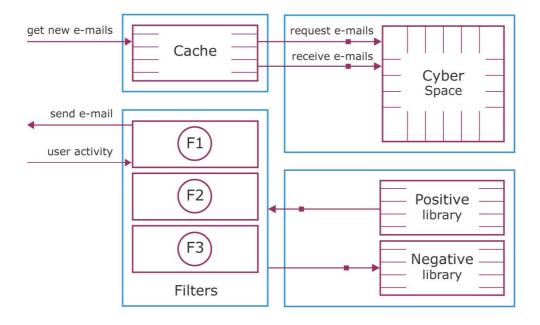

To create a schema that implements useful functionality, it should generate the lowest level primitives. You must create filters  $F = \{F_1, F_2, ..., F_i, ..., F_m\}$  that form a table of primitive relations, taken from the informational space of the planet (Fig. 2). Having a standardized data structure for the individual portals and browsers, delivering new services with higher speed you should expect a gradual qualitative improvement of all components of Cyber Space. The ultimate goal of such a mutual and positive impact of the infrastructure of cyberspace is to develop uniform standards for the interfaces and its transformation into a self-developing intelligent information computer ecosystem. Significant importance will be the primary filters or converters to create the new standardized primitives, creating a technological infrastructure for high-speed drive on the Cyber Space with the use of specialized non-arithmetic engine (I-Computer). With time, the amorphous or "garbage" of the Internet will decrease and standardized infrastructure grow. By 2020, the informational space of the planet must adopt civilized formats of data structures with standardized interfaces, just as it has happened with the development of a planetary infrastructure, transport connections to the terminals, hotels and gas stations, satisfying all user requests.

Fig. 2. The Evolution of Cyber Space and the Internet

With a specification provided after processing a verbal description in the form of a vector of input and output variables, it is easy to write a strategy to build a new functionality as the task of finding covered by the library elements of the generalized vector <X,Y>. The general solution of the problem is similar to the synthesis of an automaton model that defines the interaction of components in time and space. However, a variety of primitives are not specified in advance, excludes such a possibility, which means a shift from the strict determinism of digital machines to the field of evolutionary and quasi-solutions.

The condition of the problem: there is a specification as a vector of the essential variables that needs to cover a minimal set of primitives from the library and to generate an output vector. A beautiful solution to the problem of the functional structure synthesis of the specification is the key to self generating computer for new solutions. After the solution is solved only two problems are left on the way to the creation of computer intelligence - itself-generate original functionality required to solve the problem of coverage and specifications of new and useful for human or computer services.

# 3. Integral Metric Evaluation of the Diagnosis

Infrastructure brain-like algorithms for detecting spam includes models, methods and associative logical data structure intended to support the search process, to recognize and to make decisions based on non-arithmetic vector operations. The score is determined by solving the problem of vector-logical criterion of quality interaction between the query (a vector m) with a system of associative vectors (associates) which will generate a constructive response in the form of one or more associates and the numerical characteristics of the power supplies (quality function) input of vector m to found solution:  $\mu(m \in A)$ . The input vector  $m = (m_1, m_2, ..., m_i, ..., m_q)$ ,  $m_i \in \{0,1,x\}$  and a matrix  $A_i$  of associators

$$A_{ijr} (\in A_{ij} \in A_i \in A) = \{0,1,x\}$$

have an identical dimensionality equal q. Further the accessory level of m-vector to A vector will be designated as  $\mu(m \in A)$ .

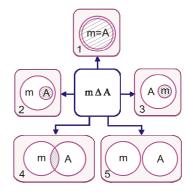

There are 5 types set-theoretic (logical)  $\Delta$  -interactions of two vectors  $m \cap A$  defined in fig. 3.

Fig. 3. The results of the intersection of two vectors

They form all primitive choices of generalized PRP-SYSTEM response (Search, Recognition and Decision making) to an input vector request. In the technology industry knowledge technical diagnostics (Design & Test) is a specified sequence of actions, it is isomorphic to the itinerary: the search for defects, their detection, the decision to restore health. All three stages of a technological route need the evaluation metric solution for the optimal choice.

Definition. Integral theoretical metric for evaluating the quality of the query is a function of the interaction of multi-valued vectors  $m \cap A$ , which is determined by the average sum of three normalized parameters: the minimum distance d(m,A), the membership function  $\mu(m \in A)$  and membership function  $\mu(A \in m)$ :

$$\begin{split} Q &= \frac{1}{3} [d(m,A) + \mu(m \in A) + \mu(A \in m)], \\ d(m,A) &= \frac{1}{n} [n - card(m_i \overset{n}{\bigcap} A_i = \emptyset)]; \\ \mu(m \in A) &= 2^{card(m \cap A) - card(A)} \leftarrow card(m \cap A) = \\ &= card(m_i \overset{n}{\bigcap} A_i = x) \& card(A) = card(\overset{n}{\bigcup} A_i = x); \\ \mu(A \in m) &= 2^{card(m \cap A) - card(m)} \leftarrow card(m \cap A) = \\ &= card(m_i \overset{n}{\bigcap} A_i = x) \& card(m) = card(\overset{n}{\bigcup} m_i = x). \\ &= card(m_i \overset{n}{\bigcap} A_i = x) \& card(m) = card(\overset{n}{\bigcup} m_i = x). \end{split}$$

Explanations. Valuation parameters allow to evaluate the level of interaction vectors in the interval [0,1]. If we set limiting maximum value of each parameter equal to 1 then the vectors are equal. Minimum score Q=0 records in the case of a complete mismatch of the vectors for all n coordinates. If the power of intersections  $m\cap A=m$  is equal to half of the space vector A, the membership function and quality are equal:

$$\mu(m \in A) = \frac{1}{2}; \ \mu(A \in m) = 1; \ d(m, A) = 1;$$

$$Q(m, A) = \frac{5}{2 \times 3} = \frac{5}{6}.$$

A similar value would be setting if the power of intersections is equal to half of the space of the vector m. If the power of intersections is equal to half of the capacity of the spaces of vectors and m, the membership functions have values:

$$\mu(m \in A) = \frac{1}{2}; \ \mu(A \in m) = \frac{1}{2}; \ d(m, A) = 1;$$

$$Q(m, A) = \frac{4}{2 \times 3} = \frac{4}{6} = \frac{2}{3}.$$

It should be noted if the intersection of two vectors is equal to empty set, the power of two characters from "empty" is taken to be zero:

$$2^{\operatorname{card}(\mathsf{m} \cap \mathsf{A}) = \emptyset} = 2^{\emptyset} = 0$$

.

It really means that the number of common points at the intersection of two spaces is zero.

The aim of introducing vector logical criteria of the solution quality is significantly improved by the performance in calculating the quality Q of interaction between the components m and A in the analysis of associative data structures by using only the vector logic operations. Arithmetic criteria (1) without averaging membership functions and minimum distance can be transformed to the form of:

$$Q = d[m, A_{i(j)}] + \mu[m \in A_{i(j)}] + \mu[A_{i(j)} \in m],$$

$$\begin{split} &d(m,A_{i(j)}) = card[m \overset{n(m)}{\underset{i(j)=1}{\oplus}} A_{i(j)} = 1]; \\ &\mu(m \in A_{i(j)}) = card[A_{i(j)} = 1] - card[m \overset{n(m)}{\underset{i(j)=1}{\wedge}} A_{i(j)} = 1]; \\ &\mu(A_{i(j)} \in m) = card[m = 1] - card[m \overset{n(m)}{\underset{i(j)=1}{\wedge}} A_{i(j)} = 1]. \end{split}$$

The first component creates the degree of mismatching n-dimensional vectors, it is the minimum distance by performing xor, the second and the third ones determines the degree of non-membership result of the conjunction to the number of units of each two interacting vectors. Notions of belonging and notbelonging are complementary but in this case it is better to calculate technological nonaffiliation. Thus, the ideal quality criteria are zero when two vectors are equal. The assessment of interaction quality between two binary vectors decreases with increasing test from 0 to 1. Finally to get away from arithmetic when you count a vector quality criteria help the expression (2) transformed to:

$$\begin{split} Q &= d(m,A) \vee \mu(m \in A) \vee \mu(A \in m), \\ d(m,A) &= m \oplus A; \\ \mu(m \in A) &= A \wedge \overline{m \wedge A}; \\ \mu(A \in m) &= m \wedge \overline{m \wedge A}. \end{split} \tag{3}$$

Here the criteria are not numbers and vectors, which evaluate the interaction of components. The increase in the number of zeros in the three vectors improves the quality criterion and the availability of units indicates the deterioration of the interaction quality.

# . Process Model of Diagnosing SPAM

Quality metric presented in (3) makes it possible to assess the proximity of spatial objects to each other as well as the interaction of the vector spaces. A practical example of the usefulness of integral quality criteria may be shooting at the goal which is illustrated by the

previously reduced diagram (see Fig. 3) of the interaction vectors:

1) The shell hit the target and did it completely. 2) The target was struck by unreasonably large caliber projectile. 3) Caliber projectile is insufficient to defeat a major purpose. 4) Inefficient and inaccurate shot by large caliber projectile. 5) The projectile flew past the target.

Process-interaction model is accompanied by integral quality criteria which evaluates not only hit or miss but also the caliber efficiency of the weapon. The analytical form of a generalized process model that selects the best interaction between the input query m to the system logic associative relationships are represented as follows:

$$\begin{split} P(m,A) &= \min Q_i(m \mathop{\triangle}^n_{\Delta} A_i) = \\ &= \vee [(Q_i \mathop{\wedge}^{\wedge}_{j=l,n} Q_j) \oplus Q_i] = 0; \\ Q(m,A) &= (Q_1,Q_2,...,Q_i,...,Q_n); \\ A &= (A_1,A_2,...,A_i,...,A_n); \\ \Delta &= \{and,or,xor,not,slc,nop\}; \\ A_i &= (A_{i1},A_{i2},...,A_{ij},...,A_{is}); \\ A_{ij} &= (A_{ij1},A_{ij2},...,A_{ijr},...,A_{msq}); \\ m &= (m_1,m_2,...,m_r,...,m_q). \\ Q_i &= d(m,A_i) \vee \mu(m \in A_i) \vee \mu(A_i \in m), \ (5) \\ d(m,A_i) &= m \oplus A_i; \\ \mu(m \in A_i) &= A_i \wedge \overline{m \wedge A_i}; \\ \mu(A_i \in m) &= m \wedge \overline{m \wedge A_i}. \end{split}$$

In order to detail the structure of vector calculations the analytical and structural process models are presented below which are given for the analysis of A matrix by columns or lines.

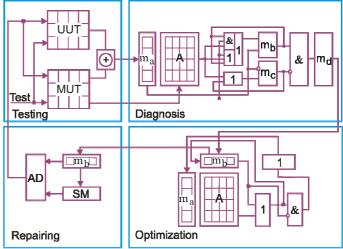

The proposed process model analysis (graph) of associative tables identified by the components of spam and introduced by the quality criteria for logical decisions that allow us to solve the problem of quasi-optimal coverage, diagnosing varieties of spam messages in an individual cyberspace (ICP) users. The model of vector calculations has provided the basis for the development of specialized multiprocessor oriented architecture search, pattern recognition and decision

making when using the associative structure of tables (Fig. 4).

Fig. 4. Model of integrated testing and restoring of ISP

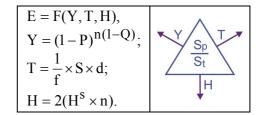

The evaluation of effectiveness (Fig. 5) of the design solution under the auspices of specialization and standardization  $\boldsymbol{S}_p \cup \boldsymbol{S}_t$  is based on the combined use of three mutually conflicting parameters: the quality Y, speed T, the program costs H:

Fig. 5. Evaluation of the effectiveness of the process model

# . Practical Results of the Implementation of Infrastructure

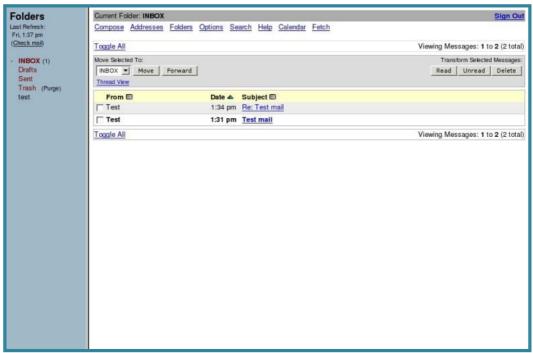

As an object of investigation was chosen SquirrelMail - email client with a Web interface written in PHP. The application can be installed virtually on any web server that has PHP installed and there is a connection to the mail server for IMAP and SMTP. The interface window is shown in Fig. 6.

Fig. 6. SquirrelMail interface

This client is easily expanding by different plugins. To conduct the study was written a plugin that implements the analysis of determination of usefulness of information based on user preferences. The process-model of the plugin is shown in Fig. 7. Based on the user's activity and the attributes of content analysis of the letter, the filter system was

selected and studied. While downloading new messages from an individual cyberspace (in this case cyberspace was presented by a subset of e-mails), the information was filtered not on the "spam" or "not spam" basis but on the basis of personal preferences of the user (Fig. 8).

Fig. 7. The process-model of the plugin for SquirrelMail

Fig. 8. Graph-scheme of the letter analysis

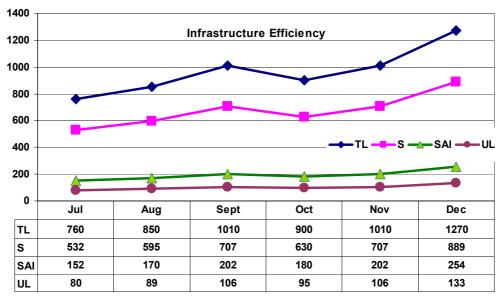

From the entire set of letters arriving at the mailbox, "spam" (anonymous mass mailings) has been partially identified not as a spam, but as distribution, which can carry out useful information for the user. Fig. 14 shows the effectiveness of introducing of the infrastructure service ICS for a single user, where the TL - Total Letters, S - Spam, SAI - Spam after Infrastructure, UL - Useful Letters. If we assume that the market attractiveness of the infrastructure is around the order of 1 billion users, the time savings in the overall market of cyberspace users is (  $T_{\scriptscriptstyle \Sigma}$  – total time savings per year ; k - the reducing ratio of spam in the implementation of infrastructure; L - the number of letters per month; N - the potential number of users in Ukraine; T - time analysis of a single letter; M number of months per year;  $H_{\Sigma}$  – the annual financial savings from the introduction of infrastructure;  $C_h$  the cost of one hour of work of a single user in

$T_{\Sigma} = k \times L \times N \times T \times M = 0,9 \times 800 \times 10000000 \times 1 \times 12 = 8640000000 \approx 2740 \text{ years} \approx 2400240 \text{ hours};$   $H_{\Sigma} = T_{\Sigma} \times C_{h} = 24002400 \times \$5 = \$120012000$

Ukraine)

Fig. 14. The effectiveness of implementation of ICS infrastructure

# . Conclusion

1. Scientific novelty of the study results is that the servicing infrastructure of individual cyberspace was proposed for the first time and characterized by the presence of built-in testing, diagnosing and restoring of

the ICS and two growing library of positive and negative messages, which gives the opportunity to significantly (by several times) reduce the analyzing time of received information.

2. *The practical* significance of the research results of infrastructure ICS service was focuses on the quality

improving of life for all stakeholders of the planet that are using email services to communicate with the outside world. In this case ICS is a model of the future of human communication with the outside world, which is invariant with respect to the technical means available in the cyberspace world. The annual economic effect from the introduction of the ICP infrastructure for Ukrainian users can make more than \$ 120 million.

3. The direction of future researches. Urgent problem is the creation of the theory, methods and architecture of the parallel analysis of information provided in the form of analysis, graph and tabular forms of associative relations for search, recognition, diagnosis and destructive components of decision making in the n-dimensional vector discrete space. It is advisable to use here a vector-logical process model of topical applications, including a diagnosis of viruses and disaster recovery software and hardware components of computer systems, the quality solutions of which are estimated by nonarithmetic metric interaction of binary vectors. Solving the problem is focused on search, detection, diagnosis of the destructive components of hardware and software by methods in discrete cyberspace. Generality of the provided theory of synthesis and analysis of cyberspace is based on the vanishing of the triad of equivalent components that are connected by xor  $m \oplus A \oplus Q = 0$  operation, formulating the conditions for solving the problem. Here, the first component m is the input code, the second A - is a destructive reference model, third Q – is the result of interaction between the first two, which may degenerate into criteria of quality relationships or decision making, the assessment of recognition of objects or images.

The goal is a substantial improvement of the quality of software products and cost reduction in operating costs due to their vaccination by introducing a code embedded software redundancy in the form of infrastructure service that provides testing, diagnosis and removal of harmful classified in libraries. The object of study is cyberspace presented by information, its carriers and converters as well as destructive components harmful to the functionality that improves the quality of human life. The subject is infrastructure of service in the form of built in redundancy program running in real time, which provides testing, diagnosis and removal of harmful components, described in the relevant libraries.

4. Expected results and its market appeal: 1) infrastructure protection of built in code from unauthorized modification, leading to a change in functionality. 2) The redundancy of infrastructure code that is automatically synthesized at the stage of design and verification is not more than 5% of the specified functionality. 3) The market attractiveness of infrastructure with the variety of software products, multiplied by the sales of each product that is equal to about one billion copies per year. 4) The cost of creating an infrastructure for software is 20% of the cost of developing functional code. If the level of sale is not less then 500 copies, the costs of creating a completely integrated antivirus payback within a year. 5) The introduction of patented software of vaccination products at their birth can bring to the company about 2 billion dollars in the first 3 years of its operation. 6) The marketing problem of global companies (Kaspersky Lab) is in persuading software developers to implement existing antivirus inside the code of useful functionality.

### . References

- [1] Infrastructure of brain-like computational processes / M.F. Bondarenko, O.A. Guz, V. I. Hahanov, J.P. Shabanov-Kushnarenko .- Kharkov: Novoe Slovo .- 2010 .- 160 p.

- [2] Designing and testing of digital systems on crystals. Verilog & System Verilog / V.I. Hahanov, E.I. Litvinov, O.A. Guz. Kharkov: KhNURE. 2009. 484 p.

- [3] Design and verification of digital systems on crystals/ V.I. Hahanov, I.V.Hahanova, E.I. Litvinova, O.A. Guz. Kharkov: Novoe Slovo. 2010. 528 p.

- [4] Semenets V.V., Hahanova I.V., Hahanov V.I. Design of digital systems using the VHDL language. Kharkov: KhNURE. 2003. 492 p.

- [5] Hahanov V.I., Hahanova I.V. VHDL+Verilog = synthesis in minutes. Kharkov: KhNURE. 2006. 264 p.

- [6] Hahanov V.I., Chumachenko S.V. Models of space in the scientific researches / Radioelectronics and Informatics. 2002. № 1. P. 124-132.

- [7] Zorian Yervant. Guest Editor's Introduction: Advances in Infrastructure IP / / <u>IEEE Design and Test of Computers</u>. 2003. P.49-55.

- [8] Bulent I. Dervisoglu. A Unified DFT Architecture for Use with IEEE 1149.1 and VSIA / IEEE P1500 Compliant Test Access Controllers. Proceedings of the Design Automation Conference. 2001. P. 53-58.

- [9] Bergeron J. Writing Testbenches using SystemVerilog. Springer US. 2006. 414 p.

Camera-ready was prepared in Kharkov National University of Radio Electronics Lenin Ave, 14, KNURE, Kharkov, 61166, Ukraine

Approved for publication: 26.08.2011. Format 60×841/8.

Relative printer's sheets: 42. Circulation: 150 copies.

Published by SPD FL Stepanov V.V.

Ukraine, 61168, Kharkov, Ak. Pavlova st., 311

Матеріали симпозіуму «Схід-Захід Проектування та Діагностування — 2011» Макет підготовлено у Харківському національному університеті радіоелектроніки Редактори: Володимир Хаханов, Світлана Чумаченко, Євгенія Литвинова Пр. Леніна, 14, ХНУРЕ, Харків, 61166, Україна

> Підписано до публікації: 26.08.2011. Формат 60×84<sup>1</sup>/<sub>8</sub>. Умов. друк. Арк. 42. Тираж: 150 прим. Видано: СПД ФЛ Степанов В.В. Вул. Ак. Павлова, 311, Харків, 61168, Україна