KHARKOV NATIONAL UNIVERSITY OF RADIOELECTRONICS

# Proceedings of IEEE East-West Design & Test Symposium (EWDTS'2012)

Copyright © 2012 by the Institute of Electrical and Electronics Engineers, Inc.

Technically Co-Sponsored by

tttc

Kharkov, Ukraine, September 14 – 17, 2012

# IEEE EAST-WEST DESIGN AND TEST SYMPOSIUM 2012 COMMITTEE

#### General Chairs

V. Hahanov – Ukraine Y. Zorian – USA

#### **General Vice-Chairs**

R. Ubar - Estonia P. Prinetto - Italy

#### **Program Chairs**

S. Shoukourian – Armenia D. Speranskiy – Russia

#### **Program Vice-Chairs**

Z. Navabi – Iran M. Renovell – France

#### **Publicity Chair's**

G. Markosyan - Armenia S. Mosin - Russia

Public Relation Chair

V. Djigan - Russia

#### Program Committee

E. J. Aas - Norway J. Abraham - USA M. Adamski - Poland A.E.Mohamed Mohamed - Egypt A . Barkalov - Poland R. Bazylevych - Ukraine A. Chaterjee - USA V. Djigan - Russia A. Drozd - Ukraine E. Evdokimov - Ukraine E. Gramatova - Slovakia A. Ivanov - Canada M. Karavay - Russia V. Kharchenko - Ukraine K. Kuchukjan - Armenia W. Kuzmicz - Poland A. Matrosova - Russia V. Melikyan - Armenia L. Miklea - Romania O. Novak - Czech Republic Z. Peng - Sweden A. Petrenko - Ukraine J. Raik - Estonia A. Romankevich - Ukraine A. Ryjov - Russia R. Seinauskas - Lithuania S. Sharshunov - Russia A. Singh - USA J. Skobtsov - Ukraine V. Tverdokhlebov - Russia V. Vardanian - Armenia V. Yarmolik - Byelorussia

#### **Steering Committee**

M. Bondarenko - Ukraine

V. Hahanov - Ukraine

- R. Ubar Estonia

- Y. Zorian USA

# **Organizing Committee**

S. Chumachenko - Ukraine

- E. Litvinova Ukraine

- V. Kharchenko Ukraine

# **EWDTS 2012 CONTACT INFORMATION**

Prof. Vladimir Hahanov Design Automation Department Kharkov National University of Radio Electronics, 14 Lenin ave, Kharkov, 61166, Ukraine.

Tel.: +380 (57)-702-13-26 E-mail: hahanov@kture.kharkov.ua Web: www.ewdtest.com/conf/

# 10<sup>th</sup> IEEE EAST-WEST DESIGN & TEST SYMPOSIUM (EWDTS 2012) Kharkov, Ukraine, September 14-17, 2012

The main target of the **IEEE East-West Design & Test Symposium** (EWDTS) is to exchange experiences between scientists and technologies of Eastern and Western Europe, as well as North America and other parts of the world, in the field of design, design automation and test of electronic circuits and systems. The symposium is typically held in countries around the Black Sea, the Baltic Sea and Central Asia region. We cordially invite you to participate and submit your contributions to EWDTS'12 which covers (but is not limited to) the following topics:

- Analog, Mixed-Signal and RF Test

- Analysis and Optimization

- ATPG and High-Level Test

- Built-In Self Test

- Debug and Diagnosis

- Defect/Fault Tolerance and Reliability

- Design for Testability

- Design Verification and Validation

- EDA Tools for Design and Test

- Embedded Software Performance

- Failure Analysis, Defect and Fault

- FPGA Test

- HDL in test and test languages

- High-level Synthesis

- High-Performance Networks and Systems on a Chip

- Low-power Design

- Memory and Processor Test

- Modeling & Fault Simulation

- Network-on-Chip Design & Test

- Modeling and Synthesis of Embedded Systems

- · Object-Oriented System Specification and Design

- On-Line Testing

- Power Issues in Design & Test

- Real Time Embedded Systems

- Reliability of Digital Systems

- Scan-Based Techniques

- Self-Repair and Reconfigurable Architectures

- Signal and Information Processing in Radio and Communication Engineering

- System Level Modeling, Simulation & Test Generation

- System-in-Package and 3D Design & Test

- Using UML for Embedded System Specification

- CAD and EDA Tools, Methods and Algorithms

- Design and Process Engineering

- Logic, Schematic and System Synthesis

- Place and Route

- Thermal, Timing and Electrostatic Analysis of SoCs and Systems on Board

- Wireless and RFID Systems Synthesis

- Digital Satellite Television

The Symposium will take place in Kharkov, Ukraine, one of the biggest scientific and industrial center. Venue of EWDTS 2012 is Kharkov National University of Radioelectronics was founded 81 years ago. It was one of the best University of Soviet Union during 60th - 90th in the field of Radioelectronics. Today University is the leader among technical universities in Ukraine.

The symposium is organized by Kharkov National University of Radio Electronics and Science of Academy Applied Radio Electronics http://anpre.org.ua/ in cooperation with Tallinn University of Technology. It is technically cosponsored by the IEEE Computer Society Test Technology Technical Council (TTTC) and financially supported by Trades Committee of Kharkov National University of Radioelectronics and Trades Committee of Students, Aldec, Synopsys, Kaspersky Lab, DataArt Lab, Tallinn Technical University.

# CONTENTS

| An Efficient Fault Diagnosis and Localization Algorithm for<br>Successive-Approximation Analog to Digital Converters<br>Melkumyan T., Harutyunyan G., Shoukourian S., Vardanian V., Zorian Y.                               | 15 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Application of Defect Injection Flow for Fault Validation in Memories<br>Amirkhanyan K., Davtyan A., Harutyunyan G., Melkumyan T., Shoukourian S.,<br>Vardanian V., Zorian Y.                                               | 19 |

| SSBDDs and Double Topology for Multiple Fault Reasoning<br>Raimund Ubar, Sergei Kostin, Jaan Raik                                                                                                                           | 23 |

| Self Compensating Low Noise Low Power PLL design<br>Vazgen Melikyan, Armen Durgaryan, Ararat Khachatryan, Manukyan Hayk,<br>Eduard Musaelyan                                                                                | 29 |

| Optimization Considerations in QCA Designs<br>Zahra NajafiHaghi, Marzieh Mohammadi, Behjat Forouzandeh, Zainalabedin Navabi                                                                                                 | 33 |

| Implementation of Address-Based Data Sorting on Different FPGA Platforms<br>Dmitri Mihhailov, Alexander Sudnitson, Valery Sklyarov, Iouliia Skliarova                                                                       | 38 |

| Comparison of Model-Based Error Localization Algorithms for C Designs<br>Urmas Repinski, Jaan Raik                                                                                                                          | 42 |

| Synthesis of Clock Trees for Sampled-Data Analog IC Blocks<br>Bilgiday Yuce, Seyrani Korkmaz, Vahap Baris Esen, Fatih Temizkan, Cihan Tunc,<br>Gokhan Guner, I. Faik Baskaya, Iskender Agi, Gunhan Dundar, H. Fatih Ugurdag | 46 |

| Experiences on the road from EDA Developer to Designer to Educator<br>H. Fatih Ugurdag                                                                                                                                      | 50 |

| Multi-Beam Constant Modulus Adaptive Arrays in Real-Valued Arithmetic Victor I. Djigan                                                                                                                                      | 54 |

| Simulation of Total Dose Influence on Analog-Digital SOI/SOS CMOS<br>Circuits with EKV-RAD macromodel<br>Petrosyants K. O., Kharitonov I. A., Sambursky L. M.,<br>Bogatyrev V. N., Povarnitcyna Z. M., Drozdenko E. S.      | 60 |

| Models for Embedded Repairing Logic Blocks<br>Hahanov V.I., Litvinova E.I., Frolov A., Tiecoura Yves                                                                                                                        | 66 |

| Real-time Interconnection Network for Single-Chip Many-Core Computers<br>Harald Richter                                                                                                                                     | 72 |

| Invariant-Oriented Verification of HDL-Based Safety Critical Systems<br>Kharchenko V., Konorev B., Sklyar V., Reva L.                                                                                                       | 76 |

| An Improved Scheme for Pre-computed Patterns in Core-based SoC Architecture<br>Elahe Sadredini, Qolamreza Rahimi, Paniz Foroutan,<br>Mahmood Fathy, Zainalabedin Navabi                                                     | 80 |

| Synthesis of Moore FSM with transformation of system in CPLD<br>Aleksander Barkalov, Larysa Titarenko, and Sławomir Chmielewski                                                                                                                                                      | 85  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| A WSN Approach to Unmanned Aerial Surveillance of Traffic Anomalies:<br>Some Challenges and Potential Solutions<br>David Afolabi, Ka Lok Man, Hai-Ning Liang, Eng Gee Lim, Zhun Shen, Chi-Un Lei,<br>Tomas Krilavičius, Yue Yang, Lixin Cheng, Vladimir Hahanov, and Igor Yemelyanov | 91  |

| Synthesis of Qubit Models for Logic Circuits<br>Wajeb Gharibi, Zaychenko S.A., Dahiri Farid, Hahanova Yu.V., Guz O.A.,<br>Ngene Christopher Umerah, Adiele Stanley                                                                                                                   | 95  |

| Theory of Optimal Nonlinear Filtering in Infocommunication's Problems<br>Victor V. Panteleev                                                                                                                                                                                         | 102 |

| Verification of Specifications in the Language L with respect to Temporal<br>Properties Expressible by GR(1) Formulas<br><b>Anatoly Chebotarev</b>                                                                                                                                   | 110 |

| Properties of code with summation for logical circuit test organization<br>Anton Blyudov, Dmitry Efanov, Valery Sapozhnikov, Vladimir Sapozhnikov                                                                                                                                    | 114 |

| Loop Nests Parallelization for Digital System Synthesis<br>Alexander Chemeris, Julia Gorunova, Dmiry Lazorenko                                                                                                                                                                       | 118 |

| Decreasing the Power Consumption of Content-Addressable Memory<br>in the Dataflow Parallel Computing System<br>Levchenko N.N., Okunev A.S., Yakhontov D.E., Zmejev D.N.                                                                                                              | 122 |

| WebALLTED: Interdisciplinary Simulator Based on Grid Services<br>Zgurovsky M., Petrenko A., Ladogubets V., Finogenov O., Bulakh B.                                                                                                                                                   | 126 |

| Malfunctions Modeling of Converters and Homogeneous-chain Distributed Structure Devices<br>Artur Gulin, Zhanna Sukhinets                                                                                                                                                             | 130 |

| On structure of quasi optimal algorithm of analogue circuit designing Zemliak A., Michua A., Markina T.                                                                                                                                                                              | 134 |

| A Neuro-Fuzzy Edge Based Spectrum Sensing Processor for Cognitive Radios<br>Mohammadreza Baharani, Mohammad Aliasgari, Mohammadreza {Najafi, Jamali},<br>Hamid Noori                                                                                                                 | 138 |

| Qubit Model for Solving the Coverage Problem<br>Hahanov V.I., Litvinova E.I., Chumachenko S.V., Baghdadi Ammar Awni Abbas,<br>Eshetie Abebech Mandefro                                                                                                                               | 142 |

| PDF testability of the circuits derived by special covering ROBDDs with gates <b>Matrosova A., Nikolaeva E., Kudin D., Singh V.</b>                                                                                                                                                  | 146 |

| Compositional Microprogram Control Unit with Operational Automaton of Transitions<br>Alexander Barkalov, Roman Babakov, Larisa Titarenko                                                                                                                                             | 151 |

| Observability Calculation of State Variable Oriented to Robust PDFs and LOC or LOS Techniques Matrosova A., Ostanin S., Melnikov A., Singh V.                                                                                                                                        | 155 |

| Low-Voltage Low-Power 2.5 GHz Linear Voltage Controlled Ring Oscillator <b>Hayk H Dingchyan</b>                                                                                                                                    | 161 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| High Speed IC Output Buffer with Reduced Power Consumption Karine Movsisyan                                                                                                                                                        | 165 |

| Engineering-Maintenance Methods of the Calculation Service Area Fixed BWA-paths<br>Sergey I. Myshlyakov, Victor V. Panteleev                                                                                                       | 170 |

| Analyses of two run march tests with address decimation for BIST procedure<br>Ireneusz Mrozek, Svetlana V. Yarmolik                                                                                                                | 176 |

| Design of Area Efficient Second Order Low Pass Analog Filter<br>Andranik Hovhannisyan                                                                                                                                              | 180 |

| Power Consumption Analysis of Content-Addressable Memories<br>Levchenko N.N., Okunev A.S., Yakhontov D.E.                                                                                                                          | 183 |

| IC Physical Design Optimization Due to Effects of Device Physical Geometries<br>Avag Sargsyan                                                                                                                                      | 187 |

| System-on-Chip FPGA-Based GNSS Receiver<br>Alexander Fridman, Serguey Semenov                                                                                                                                                      | 190 |

| Testware and Automatic Test Pattern Generation for Logic Circuits<br>Victor Zviagin                                                                                                                                                | 196 |

| Artificial Neural Network for Software Quality Evaluation Based on the Metric Analysis Oksana Pomorova, Tetyana Hovorushchenko                                                                                                     | 200 |

| Self-Compensation of Influence of Parasitic Gate-Drain Capacitances of CMOS Transistors in Analog Microcircuitry <b>Sergey G. Krutchinsky, Grigory A. Svizev, Alexey E. Titov</b>                                                  | 204 |

| Hash-based Detection of OFDM Watermarking Symbol for Radiotelephone Identification Aleksandr V. Shishkin, Aleksandr A. Lyashko                                                                                                     | 208 |

| A Novel Wideband Circular Ring DGS Antenna Design for Wireless Communications<br>Rakesh Sharma, Abhishek Kandwal, Sunil Kumar Khah                                                                                                 | 211 |

| Universal technique of the analysis of round-off noise in digital filters with<br>arbitrary structure described by topological matrixes<br>Vladislav A. Lesnikov, Alexander V. Chastikov, Tatiana V. Naumovich, Sergey V. Armishev | 215 |

| Hardware Reduction for Compositional Microprogram Control Unit Dedicated for CPLD Systems Barkalov A., Titarenko L., Smolinski L.                                                                                                  | 219 |

| Conservative Finite-difference Scheme for the Problem of Laser Pulse Propagation<br>in a Medium with Third-order Dispersion<br>Vyacheslav A. Trofimov, Anton D. Denisov                                                            | 225 |

| A Four Bit Low Power 165MSPS Flash-SAR ADC for Sigma-Delta ADC Applications<br>Hasan Molaei, Khosrow Hajsadeghi                                                                                                                    | 229 |

| Matrix Implementation of Moore FSM with Nonstandard Presentation of State Codes Titarenko L., Hebda O.                                                                                                                             | 233 |

|                                                                                                                                                                                                                                    |     |

| Alowpower1.2GS/s4-bitflashADCin0.18mCMOS<br>Mohammad Chahardori, Mohammad Sharifkhani, Sirous Sadughi                                                                                       | 237 |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Symmetrical Differential Stages on CMOS Transistors with Circuits ofSelf-Compensation and Cancellation                                                                                      |     |

| Sergey G. Krutchinsky, Grigory A. Svizev, Alexey E. Titov                                                                                                                                   | 241 |

| Lower Bound of Error in AOA Based Passive Source Localization Using Single Moving Platform <b>Hejazi F., Norouzi Y., Nayebi M.M.</b>                                                        | 245 |

| A Design for Testability Technique for Quantum Reversible Circuits<br>Joyati Mondal, Debesh K. Das, Dipak K. Kole, Hafizur Rahaman                                                          | 249 |

| A Flexible Design for Optimization of Hardware Architecture in Distributed Arithmetic based FIR Filters<br>Fazel Sharifi, Saba Amanollahi, Mohammad Amin Taherkhani, Omid Hashemipour       | 253 |

| Models for Quality Analysis of Computer Structures<br>Murad Ali Abbas, Chumachenko S.V., Hahanova A.V., Gorobets A.A., Priymak A.                                                           | 258 |

| Expanding Wireless Bandwidth in a Power-Efficient Way:<br>Developing a Viable mm-Wave Radio Technology<br>Daniel Foty, Bruce Smith, Saurabh Sinha, Michael Schröter                         | 264 |

| Sampling Theorem for Finite Duration Signal in Limited Frequency Band Gamlet S. Khanyan                                                                                                     | 270 |

| SiGe HBT Performance Modeling after Proton Radiation Exposure<br>Konstantin Petrosyants, Maxim Kozhukhov                                                                                    | 274 |

| Classical Models of Test used in Advanced Electronics Quality Assurance<br>Surendra Batukdeo                                                                                                | 278 |

| The Use of Natural Resources for Increasing a Checkability of the Digital Components in Safety-Critical Systems<br>Drozd A., Kharchenko V., Antoshchuk S., Drozd J., Lobachev M., Sulima J. | 283 |

| New version of Automated Electro-Thermal Analysis in Mentor Graphics PCB Design System <b>Petrosyants K.O., Kozynko P.A., Kharitonov I.A., Sidorov A.V., Chichkanov Y. N.</b>               | 289 |

| An Approach to Testing of Planar Integrated Antennas in Frequency Range of 5–7 GHz<br>Aleksandr Timoshenko, Ksenia Lomovskaya, Victor Barinov, Andrey Tikhomirov                            | 293 |

| Optimal project solution decision making in telecommunication systems using multicriteria optimization methods <b>Valery Bezruk, Alexander Bukhanko</b>                                     | 298 |

| Software implementation and debugging of forward error correction codes Alexey Smirnov, Danila Migalin, Ilya Muravyev, Leonid Pertsev                                                       | 303 |

| Architecture of Built-In Self-Test and Recovery Memory Chips<br>Andrienko V.A., Moamar Diaa, Ryabtsev V.G., Utkina T.Yu.                                                                    | 307 |

| The methods of exclusion of variables in symbolic time models of linear periodically time-variable circuit <b>Yuriy Shapovalov, Dariya Smal</b>                                             | 311 |

| Two-Component Encoding of Approximating Picture Pixels in Telecommunication Facilities Barannik V., Dodukh A., Safronov R.                                                                                  | 315 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Development of parameterized cell using Cadence Virtuoso<br>Vadim Borisov                                                                                                                                   | 319 |

| Simulation Methods of Diffusion Alloying Process by Means of Taurus TSUPREM-4 Programme Lagunovich N.L., Borzdov V.M.                                                                                       | 321 |

| Control and Diagnosis by Complexity Indicators of System Functioning Process<br>Tverdokhlebov V.A.                                                                                                          | 323 |

| Features of the Transfer of Information with Different Reliability in a Single Channel Alexander Bakhtin, Leonid Pertsev, Olga Timofeeva                                                                    | 327 |

| Construction of Signals with Controlled Peak-Factor<br>Koshevyy V. M., Dolzhenko D.O.                                                                                                                       | 330 |

| The Effective Method of Space Filtering of Noise in Rayleigh Communication<br>Channel with the Adaptive Antenna<br>Maistrenko G. V., Rybalko A. M., Shokalo V. M., StreInitskiy A. A.                       | 333 |

| A New Structure for Interconnect Offline Testing<br>Somayeh Sadeghi-Kohan, Shahrzad Keshavarz, Farzaneh Zokaee,<br>Farimah Farahmandi, Zainalabedin Navabi                                                  | 336 |

| Researching of Mathematical Models Based on Optimal Control Approaches for Congestion Control in Telecommunication Network <b>Lemeshko A.V., Semenyaka M.V.</b>                                             | 341 |

| Higher Order Propagation Modes Error and Its Compensation<br>Zaichenko O. B., Klyuchnyk I. I., Martynenko L. G.                                                                                             | 345 |

| Strategy of analyzing most common algorithms for path finding in discrete<br>labyrinth using software statistic data collector<br><b>Krasnov Evgeniy, Dmitry Bagaev</b>                                     | 349 |

| Method of Implementation of Technology of Orders Based Transparent<br>Parallelizing for Solving Computationally Complex Problems on Cluster<br>Vitaliy D. Pavlenko, Viktor V. Burdejnyj, Sergey V. Pavlenko | 353 |

| Scheduling Tests for 3D SoCs with Temperature Constraints<br>Indira Rawat, Gupta M.K., Virendra Singh                                                                                                       | 356 |

| Automated application mapping into Network-on-Chip topologies<br>Bykov S. O.                                                                                                                                | 360 |

| MIMO Radar with Phase-coded waveforms<br>Amirsadegh Roshanzamir, Bastani M. H.                                                                                                                              | 363 |

| BBN-based Approach For Assessment of Smart Grid And Nuclear Power Plant Interaction <b>Eugene Brezhnev, Vyacheslav Kharchenko</b>                                                                           | 367 |

| Design, Test and Fault Detection in QCA 4-to-1 Multiplexer Zahra NajafiHaghi, Behjat Forouzandeh                                                                                                            | 374 |

| The Evaluation of Statistical Characteristics of the Retransmission Meter Signal Frequency and Initial Phase on the Basis of VHDL-model <b>Dmitry A. Velychko, legor I. Vdovychenko</b>      | 378 |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| A Research of Heuristic Optimization Approaches to the Test Set Compaction<br>Procedure Based On a Decomposition Tree for Combinational Circuits<br>Valentina Andreeva, Kirill A. Sorudeykin | 382 |

| Power Reduction of 7T Dual-Vt SRAM Cell Using Forward Body Biasing<br>Sahba Sabetghadam Jahromi, Raziyeh Bounik                                                                              | 388 |

| VLSI: An Investigation into Electromagnetic Signatures (EMS) for<br>Non-Invasive Testing and Signal-integrity Verification<br>Kadim HJ, Coulibaly L. M.                                      | 392 |

| Secure Data over GSM based on Algebraic Codebooks<br>Kazemi R., Nashtaali D., Boloursaz M., Behnia F.                                                                                        | 397 |

| Simulation of Telecommunication Channel Using Volterra Model<br>Vitaliy D. Pavlenko, Viktor O. Speranskyy                                                                                    | 401 |

| Extracting Complete Set of Equations to Analyze VHDL-AMS Descriptions<br>Arezoo Kamran, Vahid Janfaza, and Zainalabedin Navabi                                                               | 405 |

| A Data Modem for GSM Adaptive Multi Rate Voice Channel<br>Boloursaz M., Hadavi A. H., Kazemi R., Behnia F.                                                                                   | 409 |

| Trends and prospects of development of techniques for extracting acoustic sounding information of the atmospheric boundary layer <b>Klyuchnik I., Panchenko A., Umyarov R.</b>               | 413 |

| Decision-Making in Robotics and Adaptive Tasks Tsymbal A.M., Bronnikov A.I.                                                                                                                  | 417 |

| Design of Nonvolatile Memory Based on Magnetic Tunnel Junction<br>for Special Electronic Systems                                                                                             |     |

| Aleksandr Kostrov, Vladislav Nelayev, Viktor Stempitsky,<br>Anatoly Belous, Arkady Turtsevich                                                                                                | 421 |

| Improving the Dependability of a Water Supply System via a Multi-Agent based CPS<br>Teodora Sanislav, Liviu Miclea, Paolo Prinetto                                                           | 425 |

| Cyber Security Lifecycle and Assessment Technique for FPGA-based I&C Systems<br>Illiashenko Oleg, Kharchenko Vyacheslav, Kovalenko Andriy                                                    | 432 |

| FPGA Technologies in Medical Equipment: Electrical Impedance Tomography<br>Perepelitsyn Artem, Shulga Dmitry                                                                                 | 437 |

| A Trend-based Design Space Exploration of Multi-core Systems Using Regression Modeling Fazeleh Hajari Taheri, Omid Fatemi                                                                    | 441 |

| Synchronous Rectifiers Enable High Efficiency for Buck-Boost Converter<br>Yurii Shynkarenko and Igor Klyuchnyk                                                                               | 445 |

| Test Data Compression Strategy While Using Hybrid-BIST methodology<br>Elmira Karimi, Mohammad Hashem Haghbayan and Mahmood Tabandeh                                                                                            | 449 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Self-Adaptive Mobile Wireless Hotspot Zones<br>Yanovsky M., Kharchenko V., Gorbenko A.                                                                                                                                         | 454 |

| The Systolic Compositions of Two-dimensional and Multidimensional Lattice Filters for Space-Time Signal Processing <b>David I. Lekhovytskiy, Andrii V. Semeniaka, and Dmytro S. Rachkov</b>                                    | 458 |

| Power Efficient Implementation of Homogenous Multi-Core Processors<br>Aram Poghosyan                                                                                                                                           | 462 |

| Assertion Based Method of Functional Defects for Diagnosing and Testing Multimedia Devices Vladimir Hahanov, Karyna Mostova, Oleksandr Paschenko                                                                               | 465 |

| Improved Scaling-Free CORDIC algorithm<br>Leonid Moroz, Taras Mykytiv, Martyn Herasym                                                                                                                                          | 470 |

| Coding Tangible Component of Transforms to Provide Accessibility and Integrity of Video Data <b>Barannik V.V., Hahanova A.V., Krivonos V.N.</b>                                                                                | 475 |

| Review of the botnet detection techniques<br>Oleg Savenko, Sergiy Lysenko, Kryshchuk Andrii                                                                                                                                    | 479 |

| MEMS Intellect Multiprobes Contacting Devices for Electrical Checking-up of Multilayers Commutative Boards and BGA/CSP Electronic Components <b>Nevliudov I.Sh., Palagin V.A., Razumov-Frizjuk E.A., Zharikova I.V.</b>        | 483 |

| Internet of Things: A Practical Implementation based on a Wireless Sensor Network Approach<br>Michele Mercaldi, Andrea D'Oria, Davide Murru, Hai-Ning Liang, Ka Lok Man,<br>Eng Gee Lim, Vladimir Hahanov, Mischenko Alexander | 486 |

| Investigation of EM Wave Propagation of the Wireless Capsule in Human Body<br>Eng Gee Lim, Zhao Wang, Jin Hui Chen, Tammam Tillo, Ka Lok Man                                                                                   | 490 |

| Using pyroelectric detectors in the design of temperature measuring devices Bondarenko A.Yu, Klyuchnik I.I.                                                                                                                    | 494 |

| Transaction Level Model of Embedded Processor for Vector-Logical Analysis<br>Irina V. Hahanova, Volodymyr Obrizan, Alexander Adamov, Dmitry Shcherbin                                                                          | 497 |

| Embedded Intelligent Control Systems on the Basis of Elementary Fuzzy-Logic Cells <b>Dontsova A., Vassiliev A.E.</b>                                                                                                           | 502 |

| Interconnection Analysis of the Integral Reliability Characteristics of the Monoergative Computer System and User's Competency <b>Krivoulya G., Shkil A., Kucherenko D.</b>                                                    | 505 |

| System approach to determination of ADC parameters<br>Knyshev Ivan                                                                                                                                                             | 511 |

| Methodological Aspects of Complex Ecological Estimation of Man-Caused Territory State and Mathematical Modelling of Processes in a Environment System Kozulia T. V., Sharonova N. V., Emelianova D. I., Kozulia M.M.           | 514 |

| Method for "Failure on Demand" Latent Faults Diagnosis of NPP Safety Control Systems<br>Gerasymenko K.E.                                                             | 519 |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Informational Saturation of Noise Signals<br>Kolodiy Z. A., Kolodiy A.Z.                                                                                             | 523 |

| The Positional Structural-Weight Coding of the Binary View of Transformants<br>Barannik V., Krasnoruckiy A., Hahanova A.                                             | 525 |

| Synchronization of a Fuzzy Automata Speranskiy Dmitriy                                                                                                               | 529 |

| Models for SoC Infrastructure of Radio Frequency Identification with Code-Division Multiple Filippenko I.V., Hahanova I.V., Filippenko I.O, Maksimov M., Chugurov I. | 535 |

| Factorization of Rhythmograms Parametric Spectra on the Base of Multiplicative Linear Prediction Models <b>Nataliia V. Kudriavtseva, Iryna O. Fil</b>                | 538 |

| Logi-Thermal Analysis of Digital Circuits Using Mixed-Signal Simulator Questa ADMS <b>Petrosyants K.O., Rjabov N.I.</b>                                              | 541 |

| Method of Hybrid Regression Analysis in the Calibration Experiments<br>Ordinartseva N. P.                                                                            | 545 |

| Keynotes speeches and Invited Reports                                                                                                                                | 548 |

| AUTHORS INDEX                                                                                                                                                        | 554 |

# **Transaction Level Model of Embedded Processor for Vector-Logical Analysis**

Irina V. Hahanova, Volodymyr Obrizan, Alexander Adamov, Dmitry Shcherbin Computer Engineering Faculty, Kharkov National University of Radioelectronics, Kharkov, Ukraine, hahanov@kture.kharkov.ua

#### Abstract

Transaction level model of embedded processor for improving the performance of logical relation analysis are proposed. It is based on the hardware implementation of vector operations. There are examples of the model using for the semantics analysis of Russian adjectives. The embedded processor was designed to be part of SoC that will be implemented on FPGA.

## Introduction

With the increase in complexity and velocity of the modern digital devices its energy consumption and cost gross also. The division of tasks across multiple cores of the processor that leads to create some parallel systems using a coherent set of specialized calculators would be a trade-off in this situation. These structures could improve the performance of solving the computational problems, and could reduce the power consumption and the hardware implementation cost of the digital systems.

The special interest of electronic technology market is the scientific and technical direction of formalizing human mental activity to create the artificial intelligence components. These intelligent tools such as expert systems, image recognition and decisionmaking need creating effective and high-speed engines (multi-processor or specialized embedded processors). A typical example of this domain that requires a specialized processor is the analysis and synthesis of the natural language constructs. At the same time one of the main points of designing the word processor is the hardware implementation of the device that handle synthesis and analysis of the language constructs.

Purpose: Development of the transaction level model of the special embedded processor for hardware realization of the vector operations.

Objectives:

1. Analysis of publications about the specialized logic processor design [1-4].

2. Analysis of the syntactic and semantic models of word processing that implement for natural languages [5-6].

3. Creation of the architecture of the specialized embedded processor that analyze the logical net of the language constructs [6].

4. The hardware implementation of the transaction level model device that implements the grammatical analysis of the Russian adjectives.

The prototype design is used the specialized device that performed grammatical analysis of adjectives end was implemented in the FPGA [6]. The proposed model has more flexibility and can handle any logical net of syntactic and semantic relations. The use of the transaction level modes and design techniques allowed to focus on the order of the data processing and transmission, and reduce unimportant details.

## 1. Transaction level modeling

With the increasing complexity of softwarehardware device such as SoC, designers need to use new digital system description models more abstract than register-transfer level (RTL) models. To address this problem, transaction level models (TLMs) were developed. TLM defines a transaction as the data transfer between sub-systems of a system. Throughout the SoC design cycle, TLM serves for three strategic activities: early software development; architecture analysis; functional verification. Modeling effort are vastly rationalized

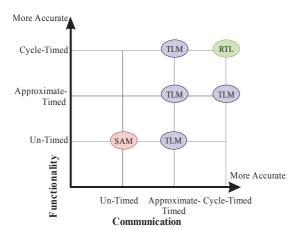

A some variation of a model developed by Dan Gajski and Lucai Cai at CODES (HW/SW Co-design Conference) 2003 [1]. The first concept is that subsystem communication and functionality can be developed and refined independently. The communication and functionality components can be un-timed (UT), approximately-timed (AT), or cycletimed (CT) (Fig. 1).

RTL model is cycle-timed accurate for communication and for functionality. System architectural model (SAM) is with un-timed communication and functionality. Approximatelytimed models can rely on statistical timing, estimated timing, or sub-system timing requirements derive from system requirements. A model with cycle-timed communication and approximately-timed functionality is Bus Functional Model (BFM). The three remaining TLM's don't have commonly accepted names. Gajski and Cai use following names:

1. Component Assembly Model - un-timed communication and approximately-timed functionality;

2. Bus Arbitration Model - approximately-timed communication and approximately-timed functionality;

3. Cycle-Accurate Computation - approximatelytimed communication and cycle-timed functionality.

Using TLM for estimations of SoC performance enable the architect to perform initial estimates right in the beginning of the project without RTL or cycleaccurate models. Early estimations enabled by real software running on TLM of SoC before RTL is available to further assist the designer.

Figure 1. Models of digital systems

Very large Verilog or VHDL simulations along with emulation strategies have traditionally been used for system-level functional verification. With increasing system complexity, Verilog and VHDL simulations have become too slow for such verification. So it is better to use the transaction level simulation for this purpose.

In addition, classes that were included in hardware description language help to improve the productivity of designer and verificater teams by organizing the code in layers, separating model and testbench code.

# 2. Model of processor for logical relation analysis

This special processor was designed to handle the logical net, where each node is a set of attributes: A, B, C (fig. 3a), and each edge is a functional relation

between two attributes that are defined as a binary table. For example, these ones could be a relation between grammatical forms of Russian adjective "stress" – "word stem" that belongs to adjective logical network [6].

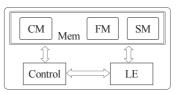

Figure 2 shows the framework special embedded processor that consists of three main units: Control block (Control), Logical block (LE), and Memory block (Mem). In turn the last one includes following components: a command memory, a function memory, and a set memory.

Figure 2. Processor framework

The advantage of the proposed embedded special processor model is that it was constructed to handle the logical nets of any dimensions and doesn't depend on the length of the set vectors and the sizes of the relation tables. It has only limitation that is defined by physical memory size.

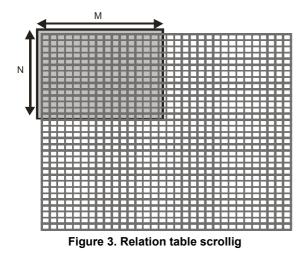

The Logical block receives the data parts of a fixed size. If relation table or set vector has bigger size than memory buses dimension, they are broken apart. So there used window scrolling to traverse through whole table (fig 3). The size of scroll window is determined by the memory bus size that transferring data between memory and logic blocks. Process of table starts with the upper-left corner and finishes in the right-down corner. The number of steps for process a table with the NxM dimension are described by equations  $N_R$  =  $Nn \cdot Nm$  . Each relation table after dividing by 2D slice are stored in memory as 1D vectors. Similarly the set vectors are split on the memory words and stored in the memory by parts. Two separated memory blocks that storing relation tables and set vectors allow to read in one cycle two parts of date that are need to implement the elementary logical operation.

For example, if the size of the scrolling window equals 4x4, the relation table with the dimension 26x13 would be split on 28 blocks. It means the processing of this table would need 28 elementary logical operations that make up the processing cycle of the table.

Assume the relations table has a size of 2 to 7 and has following contents.

| 1 | 1 | 1 | 0 | 1 | 0 | 1 |  |

|---|---|---|---|---|---|---|--|

| 0 | 0 | 0 | 1 | 0 | 1 | 0 |  |

| 1 |   |   |   |   | 2 |   |  |

|   | ' |   |   |   |   | ~ |  |

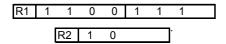

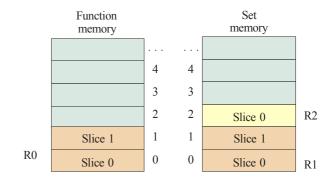

If size of the scrolling window is 4x4 so this table would take two 16 bit words (fig 4) of the Function memory.

The set vectors are binary where 1 means that the element is included in the set and 0 that it isn't. If relation table dimension is 2x7, the sizes of vectors are 2 and 7 bits, respectively. So R2 vector needs to store 1 memory word, and R1 vector needs 2 words (fig 5). For example,

Command memory uses following format of the word.

where size\_W and size\_H define the size of the relation table, addr\_R0, addr\_R1, and addr\_R2 are start addresses of the date blocks. For the example above and according to Figure 6, the command memory word will have value

| 0 | - | <u>^</u> | <u>^</u> | 0 |

|---|---|----------|----------|---|

| 2 | 1 | 0        | 0        | 2 |

Figure 4. Memory that storing one relation table and its set vectors

# 3. The transaction level model of the processor

By the classification [1] the proposed model of the special embedded processor is with approximated time accurate for communication and for functionality, so it is the Bus Arbitration Model.

Object Oriented Programming (OOP) was used for developed the processor model. Each device unit was designed as class that communicates with the other ones through virtual interface. Then for refining design these classes could be replaced by a description of RTL-level, and the virtual interface could be changed to interface block.

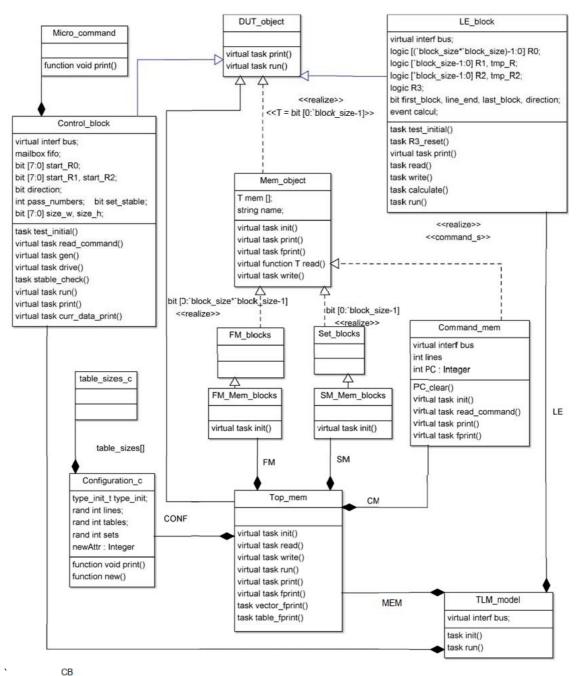

For the developing of transaction level model are used object-oriented language features of the SystemVerilog hardware description and verification. Figure 6 shows the structure of the classes.

TLM\_model includes objects of three classes: Control\_block, LE\_block, and Top\_mem, which describe the three units of the embedded processor framework (fig. 2): Control block (Control), Logical block (LE), and Memory block (Mem).

Base class is DUT\_object class (fig. 6). Other classes expanded upon its through inherence. The Configuration class is designed to control the constraint random generation of the input stimuli that is used at the verification stage.

Micro\_command encapsulate the data together with the routines that describe and manipulate processor commands. Mem\_object class is blueprint The classes that describe memory have the methods: for variable value initial (read and write), for output data to the consol (print); for output data to text file (fprint); for work starting (run). In addition to these methods the Control block that is described as the class control\_block, has routines: for reading a command (read\_command), for generating the control signal sequences for memory and logic unit (gen), for transmitting control signals through the interface (drive). Stable\_check () method checks the time of the finishing of the logical net processing.

An object of the TLM\_model class is implemented in the Top module that includes the bus interface also. The last one is a model of the special embedded processor bus. The SystemVerilog code of the interface is shown on listing 1. Also it has variable that describe transmitting data as well as events that synchronize the work of individual blocks of the system.

#### Listing 1. SystemVerilog model of the interface interface interf;

bit clk = 0; initial forever #5 clk = ~clk;

//command event command\_request; event command\_resp; event PC\_clear\_e; event pass\_end; // pass all commands event work\_stop; // bit [7:0] size\_r1, size\_r2;

bit [7:0] start\_R0, start\_R1, start\_R2; clocking cb@(posedge clk);

// output size\_r1, size\_r2;

// output start\_R0, start\_R1, start\_R2;

endclocking: cb always @(pass\_end) \$display("1 pass command memmory have finished");

// memmory

event data\_read, data\_send, pass\_start;

bit [7:0] addr\_R0, addr\_R1, addr\_R2;

bit first\_block, line\_end, last\_block, direction;

logic [(`block\_size\*`block\_size)-1:0] R0;

logic [`block\_size-1:0] R1;

logic [`block\_size-1:0] R2;

bit R3;

event data\_write;

bit [7:0] addr\_R2\_w;

logic [`block\_size-1:0] R2\_w;

// stop

event simul\_finish; endinterface

## 4. Conclusion

Scientific novelty. The transaction level model of the special embedded processor for logical analysis of the Russian adjectives was developed. The model allows creating the hardware implementation for any logical relations graph for natural language structure analysis. This device requires more time for processing of the system than one that was presented earlier [6], but exceeds it in versatility.

The object-oriented programming has been used to reduce the design time of creating the SystemVerilog transaction level model. This modern approach of the development of the digital systems significantly improves the design process performance.

Further studies are associated with the creating the generators of the complex architecture of the logical relations, with the possibility of combining several logic blocks to improve the functional performance.

## 5. References

[1] David C. Black, Jack Donovan. SystemC: from the ground up. Kluwer Acad. Publishers, 2004. 263p.

[2] Bergeron, Janick. Writing testbenches: functional verification of HDL models. Boston: Kluwer Academic Publishers, 2001. 354 c.

[3] Donald E. Thomas. Philip R. Moorby. The Verilog Hardware Description Language. New York, Boston, Dordrecht, London, Moscow: Kluwer Academic Publishers. 2002. 404 p.

[4] Hahanov V.I., Hahanova I.V. and others. Verilog&SystemVerilog. Kharkov: New word, 2010. 528c.

[5] General algebra. Handbook. V.2. Ed. Skornyakova. 1991. chapter 7. Categories. M. Nauka. 1991. P.368-460.

[6] Bondarenko M.F., Hahanova I.V. Logic networks application for computing process organization. Radioelectronics & Informatics, 2003. P. 150-156.

Figure 5. Model of classes

Camera-ready was prepared in Kharkov National University of Radio Electronics Lenin Ave, 14, KNURE, Kharkov, 61166, Ukraine

> Approved for publication: 27.08.2012. Format 60×841/8. Relative printer's sheets: 49. Circulation: 200 copies. Published by SPD FL Stepanov V.V. Ukraine, 61168, Kharkov, Ak. Pavlova st., 311

Матеріали симпозіуму «Схід-Захід Проектування та Діагностування – 2012» Макет підготовлено у Харківському національному університеті радіоелектроніки Редактори: Володимир Хаханов, Світлана Чумаченко, Євгенія Литвинова Пр. Леніна, 14, ХНУРЕ, Харків, 61166, Україна

> Підписано до публікації: 27.08.2012. Формат 60×84<sup>1</sup>/<sub>8</sub>. Умов. друк. Арк. 49. Тираж: 200 прим. Видано: СПД ФЛ Степанов В.В. Вул. Ак. Павлова, 311, Харків, 61168, Україна