## MINISTRY OF EDUCATION AND SCIENCE OF UKRAINE KHARKOV NATIONAL UNIVERSITY OF RADIOELECTRONICS

ISBN 966-659-088-3

# Proceedings of East-West Design & Test Workshop (EWDTW'04)

Yalta, Alushta, Crimea, Ukraine, September 23 – 26, 2004

© Kharkov National University of Radioelectronics, 2004

### CONTENTS

| EDUARDAS BAREISA, VACIUS JUSAS, KESTUTIS MOTIEJUNAS, RIMANTAS SEINAUSKAS.<br>THE TESTING APPROACH FOR FPGALOGIC CELLS                                            | 8   |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| T. TONNISSON, L. KUUSIK. DATA ACQUISITION MODULE FOR OPTICAL<br>TELECOMMUNICATION TEST INSTRUMENT                                                                | 15  |

| H.J. KADIM. CONDITIONAL ASSERTION OF EVENTS WITH APPLICATIONS TO VERIFICATION OF SOC                                                                             | 17  |

| TOMASZ GARBOLINO, ANDRZEJ HLAWICZKA, ADAM KRISTOF. ANEW IDEA OF<br>TEST-PER-CLOCK INTERCONNECT BIST STRUCTURE                                                    | 23  |

| M. BRIK, J. RAIK, R. UBAR, E. IVASK. GA-BASED TEST GENERATION FOR SEQUENTIAL<br>CIRCUITS                                                                         |     |

| JAAN RAIK, PEETER ELLERVEE, VALENTIN TIHHOMIROV, RAIMUND UBAR. FAST FAULT<br>EMULATION FOR SYNCHRONOUS SEQUENTIAL CIRCUITS                                       | 35  |

| ELENA FOMINA, ALEXANDER SUDNITSON. INFORMATION RELATIONSHIPS FOR<br>DECOMPOSITION OF FINITE STATE MACHINE                                                        | 41  |

| JACEK WYTRÊBOWICZ. AGENTIS VALIDATION – A CASE STUDY                                                                                                             | 48  |

| GENNADIY KRIVULYA, ALEXANDR SHKIL, YEVGENIYA SYREVITCH, OLGAANTIPENKO.<br>VERIFICATION TESTS GENERATION FEATURES FOR MICROPROCESSOR- BASED<br>STRUCTURES         | 57  |

| SHALYTO A.A., NAUMOV L.A. NEW INITIATIVE IN PROGRAMMING.<br>FOUNDATION FOR OPEN PROJECT DOCUMENTATION                                                            | 64  |

| ROMANKEVYCH A., ROMANKEVYCH V., KONONOVA A. SOME CHARACTERISTICS<br>OF FTCS MODELS' BEHAVIOR (IN THE FLOW OF FAULTS)                                             | 69  |

| BOICHENKO Y.P., ZAYCHENKO A.N. IMPLEMENTATION EXPERIENCE OF DSP<br>APPLICATIONS USING FPGA ARCHITECTURE. RESEARCH OF PRACTICAL                                   |     |

| METHODS FOR IMPROVING LOGIC STRUCTURES                                                                                                                           | 70  |

| DROZD A., SITNIKOV V. AN ON-LINE TESTING METHOD FOR A DIGIT BY DIGIT<br>PIPELINE MULTIPLIER WITH TRUNCATED CALCULATIONS                                          | 76  |

| SAPOSHNIKOV V., SAPOSHNIKOV VL., MOROZOV A, OSADTCHI G., GÖSSEL M.<br>DESIGN OF TOTALLY SELF-CHECKING COMBINATIONAL CIRCUITS BY USE<br>OF COMPLEMENTARY CIRCUITS | 83  |

| V. ZAGURSKY, A. RIEKSTINCH. BIST FOR HIGH SPEED ADC                                                                                                              |     |

| V. ZAGURSKY. I.ZARUMBA, A.RIEKSTINCH. A STATISTICAL METHOD FOR<br>ANALOG-DIGITAL SYSTEM TESTING IN TIME AND SPECTRAL DOMAIN                                      |     |

| A. CITAVICIUS, M. KNYVA. MEASUREMENT INSTRUMENTS SOFTWARE<br>REQUIREMENTS                                                                                        | 97  |

| THOMAS KOTTKE, ANDREAS STEININGER A DUAL CORE ARCHITECTURE WITH ERROR<br>CONTAINMENT                                                                             | 102 |

| ORESTA BANDYRSKA, MARTA TALAN, VOLODYMYR RIZNYK. APPLICATIONS OF<br>THE PERFECT COMBINATORIAL SEQUENCES FOR INNOVATIVE DESIGN AND TEST                           | 109 |

| BAZYLEVYCH R.P., PODOLSKYY I.V. INVESTIGATION OF PARTITIONING<br>OPTIMIZATION BY THE OPTIMAL CIRCUIT REDUCTION METHOD                                            | 113 |

| VOLODYMYR G. SKOBELEV. NON-STATIONARY SECRET LOCK: MODEL<br>AND CHECKING                                                                                         | 117 |

| SKOBTSOV Y.A., SKOBTSOV V.Y. EVOLUTIONARY METHODS OF THE TEST<br>PATTERN GENERATION FOR DIGITAL SYSTEMS AT DIFFERENT PRESENTATION                                                    |     |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| LEVELS                                                                                                                                                                               | 123 |

| A. MATROSOVA, S. OSTANIN , A. VORONOV. DESIGNING FPGA-BASED SELF-TESTING<br>CHECKERS FOR ARBITRARY NUMBER OF UNORDERED CODEWORDS                                                     | 130 |

| SHARSHUNOV S.G., BELKIN V.V. FUNCTIONAL TESTING OF MICROPROCESSORS.<br>CASE STUDY                                                                                                    | 135 |

| SAMOILOV V.G., SPERANSKIY D.V., KUPRIYANOVA L.V. DIAGNOSTIC PROBLEM FOR<br>LINEAR AUTOMATA IN INTERVAL STATEMENT                                                                     | 142 |

| EVGENY V.GALICHEV, SERGEY A.KOLOMIETS, VLADIMIR LANTSOV.<br>ARCHITECTURE OF FPGA PROGRAMMING FOR PROTOTYPING TASKS                                                                   | 149 |

| M. SKVORTSOV, M. SERINA, S. MOSIN. AUTOMATED TESTING OF SOFTWARE SYSTEMS                                                                                                             | 150 |

| S.À. KOLOMIETS, I.À. KOLOMIETS, V.N. LANTSOV. DESIGN OF ADPCM-CODEC<br>ON FPGA BASIS                                                                                                 | 152 |

| KONSTANTIN KULIKOV. IP CORES USING FOR CREATION COMPLEX SYSTEM ON A CHIP                                                                                                             | 155 |

| MICHAEL A. TROFIMOV. THE SUBSYSTEM FOR AUTOMATING OF MODEL<br>GENERATION ON VHDL-AMS                                                                                                 | 157 |

| I. A. KOLOMIETS, E. B. KOBLOV, K.V. KULIKOV. RESEARCH OF THE SPEECH SIGNAL PREDICTOR                                                                                                 | 159 |

| N. KASCHEEV, Y. RYABKOV, S. DANILOV. TEST GENERATION FOR SYNCHRONOUS<br>DIGITAL CIRCUITS BASED ON CONTINUOUS APPROACH TO CIRCUIT MODELING                                            | 161 |

| B. SOKOL, I. MROZEK, V. N. YARMOLIK. TRANSPARENT MARCH TESTS TO EFFECTIVE PATTERN SENSITIVE FAULTS DETECTION                                                                         | 166 |

| A.A. USHAKOV, V.S. KHARCHENKO.<br>V.V. TARASENKO. METHODS OF MODELING AND<br>ERROR-TOLERANT DESIGN OF DEPENDABLE EMBEDDED SOPC/FPGA-DECISIONS<br>BY USE OF MULTIVERSION TECHNOLOGIES | 172 |

| A.A. BARKALOV, I.J. ZELENYOVA. RESEARCH OF MULTI-LEVEL STRUCTURE OF THE CONTROL UNIT IN THE BASIS OF PLD                                                                             | 179 |

| E. BUSLOWSKA, V. N. YARMOLIK. TWO-DIMENSIONAL COMPACTION TECHNIQUES<br>FOR RAM BIST                                                                                                  |     |

| ROMAN KVETNY, VLADIMIR LYSOGOR, ALEKSEY BOYKO. INTERVAL MODELLING<br>OF COMPLEX SYSTEMS                                                                                              |     |

| BARKALOV A.A., BUKOWIEC A.F., KOVALYOV S.A. SYNTHESIS OF MEALY FSM WITH<br>MULTIPLE ENCODING OF INTERNAL STATES                                                                      | 193 |

| <b>DOROFEEVA M.U., PETRENKO A.F., VETROVA M.V., YEVTUSHENKO N.V.</b> ADAPTIVE TEST<br>GENERATION FROM A NONDETERMINISTIC FSM                                                         | 197 |

| LADYZHENSKY Y.V., POPOFF Y.V. A PROGRAM SYSTEM FOR DISTRIBUTED<br>EVENT-DRIVEN LOGIC SIMULATION OF VHDL-DESIGNS                                                                      | 203 |

| O. NEMCHENKO, G. KRIVOULYA. USE OF PARALLELISM IN FINITE STATE MACHINES.<br>MATHEMATICAL LEVEL                                                                                       | 210 |

| VOLODYMYR NEMCHENKO. NETWORK SAFETY. PROBLEMS AND PERSPECTIVES                                                                                                                       | 214 |

| KOLPAKOV I.A., RYABTSEV V.G. OPERATIONS OF TRANSFORMATION OF VECTORS<br>INFLUENCES COORDINATES AT DIAGNOSING MODERN DIGITAL SYSTEMS                                                  | 217 |

| RYABTSEV V.G., KUDLAENKO V.M., MOVCHAN Y.V. METHOD OF AN ESTIMATION                                                                            |     |

|------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| DIAGNOSTIC PROPERTIES OF THE TESTS FAMILY MARCH                                                                                                |     |

| MIKHAIL ALEXANDROVICH LODIGIN. THE NEW OPERATIONAL MODE FOR DIGITAL OSCILLOSCOPES                                                              | 225 |

| T.V. GLADKIKH, S. YU. LEONOV. K-VALUE DIFFERENTIAL CALCULUS CAD                                                                                | 227 |

| S.A. ZAYCHENKO,A.N. PARFENTIY, E.A. KAMENUKA, H. KTIAMAN. SET OPERATION<br>SPEED-UP OF FAULT SIMULATION                                        | 231 |

| <b>VOLKER HW. MEYER, AJOY K. PALIT, WALTER ANHEIER.</b> EVALUATION OF SIGNAL<br>INTEGRITY TESTS BASED ON TRANSITION DELAY FAULT TEST PATTERN   | 238 |

| <b>V. A. TVERDOKHLEBOV.</b> THE GENERAL FEATURES OF GEOMETRICAL IMAGES<br>OF FINITE STATE MACHINES                                             | 243 |

| CHUMACHENKO S.V., GOWHER MALIK, KHAWAR PARVEZ. REPRODUCING KERNEL<br>HILBERT SPACE METHODS FOR CAD TOOLS                                       | 247 |

| BONDARENKO M.F., DUDAR Z.V. ABOUT 'SIMILAR-TO-BRAIN' COMPUTERS                                                                                 |     |

| CHIKINA V.A., SHABANOV-KUSHNARENKO S.Y. ABOUT MODIFIED CATEGORIES                                                                              |     |

| M. KAMINSKAYA, O.V. MELNIKOVA, SAMI ULAH KHAN, W. GHRIBI. IMPROVING TEST<br>QUALITY BY APPLYING BOUNDARY SCAN TECHNOLOGY                       | 263 |

| S. HYDUKE, A.A. YEGOROV, O.A. GUZ, I.V. HAHANOVA. CO-DESIGN TECHNOLOGY<br>OF SOC BASED ON ACTIVE-HDL 6.2                                       | 269 |

| KAUSHIK ROY. DESIGN OF NANOMETER SCALE CMOS CIRCUITS                                                                                           | 273 |

| V.I. HAHANOV, V.I. OBRIZAN, A.V. KIYASZHENKO, I.A. POBEZHENKO. NEW FEATURES<br>OF DEDUCTIVE FAULT SIMULATION                                   | 274 |

| LANDRAULT CHRISTIAN. MEMORY TESTING                                                                                                            | 281 |

| SAMVEL SHOUKOURIAN, YERVANT ZORIAN. EMBEDDED-MEMORY TEST AND REPAIR:<br>INFRASTRUCTURE IP FOR SOC DEBUG AND YIELD OPTIMIZATION                 |     |

| <b>A.V. BABICH, I.N. CHUGUROV, YE. GRANKOVA, K.V. KOLESNIKOV</b> . PLANNING OF PASSIVE EXPERIMENT FOR EXPLICIT FAULTS AND BOTTLENECKS LOCATION |     |

| BENGT MAGNHAGEN. ELECTRICAL TEST IS NOT ENOUGH FOR QUALITY                                                                                     |     |

### CO-DESIGN TECHNOLOGY OF SOC BASED ON ACTIVE-HDL 6.2

### S.HYDUKE, A.A. YEGOROV, O.A. GUZ, I.V. HAHANOVA.

Design Automation Department, Kharkov National University of Radio Electronics, Lenin ave, 14, Kharkiv, 61166 Ukraine. E-mail: hahanov@kture.kharkov.ua

It is represented technology of designing and verification of digital systems-on-a-chip (SoC), based on the experience of design of hardware and software components of SoC in one environment. It reflects today situation of variety of available silicon, software and hardware description languages, design tools. There are also presented recommendations and examples.

### 1. Today's market of design technologies

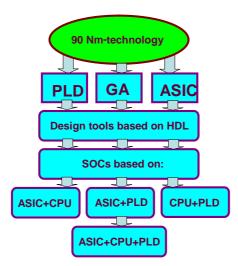

On today's EDA market there are 3 major target silicon technologies that define computer world today – programmable devices, gate arrays and ASICs. They and relations between them are presented on Fig. 1.

That includes manufacturing technology of silicon chips, hardware and software description languages, design tools, SoC methodology.

Fig. 1. Cause-effect relation on the EDA market

Practical explanation of presented figure is that because of influence of SoC on ASIC and FPGA (PLD) designs it is started integration between them. On FPGA's started to appear powerful embedded processors such as ARM and PowerPC. For example latest Xilinx Virtex II Pro FPGA is 4 embedded IBM PowerPC processors plus 10 million of programmable gates available for user. Design flows of FPGAs and ASICS also started to merge after announcing by Altera Structured ASIC flow. Where FPGA verified design is transferred to ASIC without any participation of the developer.

That will influence world chip market – that is about \$40 billions per year: 1) powerful processors, that are used on servers and working stations; 2) personal computers area, where Intel processors holding the leading place with \$20 billions; 3) microcontrollers and signal processes generate to vendors \$14 billion revenue every year. The 3<sup>rd</sup> segment is the most growing one from all three. Hardware development reached stage that number of transistors is growth is 60% per year, but their usage in project growing only 20% per year. That's why we can see today rapid growth of number of SoCs. On that available space on a chip are transferred from the board all buses and peripherals of the developed system. That allows not only increasing productivity of whole digital system and make it with custom functionality, but significantly to reduce energy consumption and decrease physical size of final product. At the same time one of the main requirements of designing complex systems today is to use module approach. Where designer can reuse modules from previous projects or use IP-(Intellectual Property)-core. For SoCs there are bunch of various ready to use processors with peripheral buses and libraries of standard peripherals. With different functionality, sizes, from simple interface to complicated 64bit processors that requires couple of millions transistors.

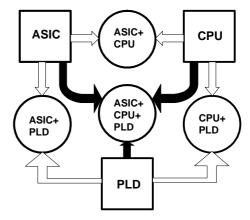

According to Fig.2 variety of silicon solutions of

Fig. 2. Types of chips

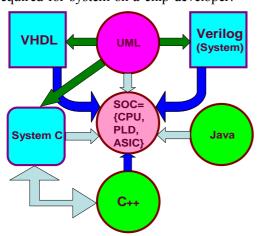

implementing SoC depends on 3 basic components and all possible combinations between them, that make full set of available on the market components that can satisfy almost every customer. Based on chip technologies available on the microelectronics market the most effective by performance are ASIC: ASIC -Application-Specific Inegrated Circuit-custom IC's, that usually developed by one company for specific need. For example Analog Devices, Infineon, Motorola, Qualcomm, Texas Instruments, EPSON, NEC, others. Such oriented IC's in thousand times are more effective by cost and performance per watt then processors and also significantly reduce board sizes and number of its components. But specialpurpose IC's do not have flexibility of reconfiguring. And second disadvantage is the high price of developing and manufacturing ASICs (millions of USD). Reconfigurable PLDs have very high costs per chip but can be purchased in very small volumes. That makes them very attractive for big number of digital systems developers (about 2 billions USD market). Especially when world leading companies in PLD for SoC area Altera and Xilinx enhancing PLDs today with softcore (Xilinx PicoBlaze, MicroBlaze; Altera Nios) and embedded processors as PowerPC and ARM; rocket I/ O's, big embedded memory blocks. Latest FPGAs start to be serious alternative to the powerful "fixed" logic. Variety of proposed electronic solutions require proper set of design tools, based on the hardware description languages and software products, that fully or maximally close support IEEE standards. On figure 3 it is presented structure of languages required for system-on-a-chip developer:

Fig. 3. Language support

Here the dominant group is (Verilog, VHDL, SystemC). They will exist for 5 more years together, competing and supplement each other. Availability of compilers for every of them and also mixed languages simulators allow successfully to use multiple languages blocks in one project together. Such technology is supported by major Electronic Design Automation (EDA) companies (Cadence, Synopsys, Mentor Graphics, Aldec)

Further enhancement receives Unified Modeling language (UML) [7], that is targeted on creation of models and verification of heterogeneous systems. It is enough to say that on 41<sup>st</sup> DAC'04 whole day was dedicated for discussions to this language in terms of workshop [DAC'04]. Languages C++ and Jawa, oriented on software development for embedded processors of SoC's as ARM, PowerPC, MIPS, others; and on writing modules that participate in logic simulation via programming language interface (PLI) for better and easier debugging and verification.

# 2. Verification technology of System-on-Chip

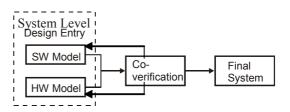

Main target – is to create regulated sequence of actions that allows practically utilize software/ hardware co-design solution, presented on figure 4.

To achieve that, 2 main decisions should be made:

1) Creation of the universal model (system level) for design and verification [8,9,10,11] Hardware+Software for SoC, that includes base silicon (PLD, ASIC) and CPU.

2) Configuration of design tools of leading industry vendors that allow finding acceptable SoC or Final System solution by development time, design costs, performance. (see Fig. 4.)

Fig. 4. Model of design process

Following points should be considered as main principles of designing:

1. It is necessary to support several types of specification formalization on the basis of standard hardware description languages.

2. To utilize description method that is more preferable for adequate representation of the project fragment function.

3. To utilize already verified IP-cores blocks

4. To design own logic blocks in way that they can be easily reused in next designs (design reuse)

5. To verify correct functionality by simulation/ emulation whole HW/SW system with embedded processor/processors, IP-cores, user designed blocks, system software in co-simulation environment. Deep HW and SW debug can prevent a lot of further design re-spin cycles and is very important on this stage.

6. To analyze software/hardware behavior components in real time environment.

# **3.** Aldec co-verification technology for ARM based SoCs

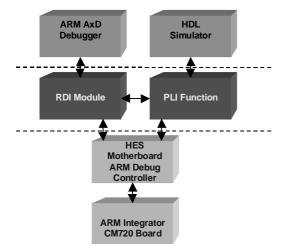

In this technology it is used hardcore ARM processor connected to HES-board via AMBA bus [12,13] for purpose of accelerating of logic simulation (Fig. 5) of whole system. HES-board has FPGA chip/chips on it with programmed user logic.

Fig.5. General model of SOC verification process

Here on fig. 5 it is represented general structure of software/hardware components used in design and verification of the system on a chip in Aldec Inc. Four upper blocks are – software products:

1) ARM AxD Debugger for C++/Assembly system software, that works on real time systems and allows to stop simulation on user specified breakpoints, view variables, registers, memory.

2) HDL simulator – in this case it is Active-HDL v.6.2.

3) RDI Module.

4) PLI functions that provide connection and synchronization of the first two blocks and hardware.

5) Hardware Embedded Simulation (HES) board with attached via connectors ARM Integrator CM720 Board. On HES board there is available reconfigurable logic (FPGAs), memory that can be programmed by blocks of user logic and can participate in simulation together with logic simulator. ARM integrated board contains ARM processor that is used in simulation of developed SoC based on ARM processor.

Such configuration significantly increases performance of the debug process of system software (C++/Assembly code) in comparison with methodology of utilizing C-model of ARM processor during logic simulation. So block 1 is oriented on the design entry and verification of the system software. Block 2 is required for design entry and debug of hardware part of the system, described on HDL and representing peripheral modules of the system, that are usually work under control of system software executing on the ARM processor.

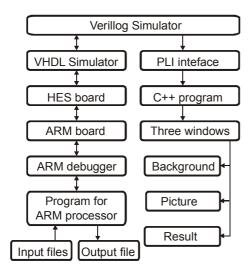

Figure 6 illustrates example, where sequence of operations for achieving main goal – hardware implementation of superposition of 2 video streams and their output to the screen.

Conseptual flowgraph of the algorithm (14 states), implemented with the help of Active-HDL v.6.2 [14], is presented on figure 8. Basically it is control machine for the operational unit of the superposition of video streams.

Main functions of designed SoC:

1. Opening of 2 AVI files. One of them is "main animation", other one is – "background".

2. Opening 2 frames from opened files.

3. Locating opened frames in the memory on the HES board through peripherals and AMBA bus.

4. Superposition of the frames with the purpose of the uniting images and writing results back to file on a disk.

5. Forming 3 streams of data that deliver 3 video windows with the 2 basic video streams and with result one, after superposition of initial ones. Windows are displayed on workstation through

EWDTW'T004

PLI routines connected to the system under simulation.

Fig. 6. Model of the design process of the SOC

Following design and verification tools were used: Hardware: HES board 2000; ARM daughter board. Software: Aldec Active-HDL 6.2; ARM Device Suite; Alatek DVM; Xilinx ISE 5.2; Microsoft Visual Studio .NET 2003. PLI interface was used to attach library of functions that were used for nice visualization output results of the system during simulation. For the connection of the peripherals and processor it was used AMBA ASB bus standard. It is 32 bit bus that is widely used in SoC devices based on ARM processor. It provides data flow between processor and peripheral devices.

The system is functioning in the following way: after two AVI files with the same number of frames are opened, the superposition or overlay of their contents is performed and the resulting image is displayed in three separate windows.

It is important to partition functions on software and hardware ones during designing of the system level of the embedded system. In this case it is stimulates to achieve processor controlled system with the high performance at the end of design cycle.

To increase speed of drawing frames on the screen (up to 24 frames per second) it is used RLE8- compression format. This allows to reduce data flow going through AMBA bus, and to make system and visualization to run faster.

In case if there is no available hardware with ARM processor and interface to logic simulator

it can be used SystemC model instead. Same system for verification was implemented with Synopsys System C Studio on Solaris OS.

### 4. Conclusions

Main results that form science and practical meaning for design and verification of systemon-a-chip and should be underlined are:

1. It is presented overview of tools and methods in area of design and verification of digital systems on a chip, including hardware description languages and software products, and also technologies and types of chips available on the electronic technologies market.

2. It is offered technology of designing of software/ hardware tools on the basis of the hardware acceleration that allows to reduce significantly (in 2-10 times) simulation and verification time.

3. It is presented technology of co-verification of hardware and software components of digital system on the basis of utilization together logic simulator, C++/Assembly debugger and hardware accelerator. That allows effectively verify designing digital SoC.

4. It is presented an example of verification of digital device that perform superposition of video streams in one with the output of the result during simulation on the screen through Program Language Interface (PLI) [15]. System is based on the ARM processor, C++ debugger and Active HDL program simulator,

5. It is suggested to utilize video stream as effective test approach to testing of the functions of the autonomously designed digital device. That visually allows seeing "bugs" right on a screen in case if they present in some components of the system and also test all its functions on working frequencies.

References: 1. Bass M.J. and Cristensen C.M. The future of the Microprocessor Business.- IEEE Spectrum, April, 2002, P. 34-39. 2. Don Edenfeld, Andrew B Kahng, Mike Rodgers, and Yervant Zorian, "2003 Technology Roadmap for Semiconductors", Computer, Janvary 2004, pp. 47-56. 3. Nick Tredennock, Brion Shimamoto. "Go Reconfigure". IEEE Spectrum. December 2003. P. 37-40. 4. B. Gupta and M. Borgatti. Different Approaches to Add Reconfigurability in a SoC Architecture // Design Automation and Test in Eurpe (DATE 03).- 2003.- P. 398-402. 5. M. Borgatti, L. Calì, G. De Sandre, B. Forêt, D. Iezzi, F. Lertora, G. Muzzi, M. Pasotti, M. Poles, P.L. Rolandi (STMicroelectronics) A Reconfigurable Signal Processing IC with Embedded FPGA and Multi-Port Flash Memory // Design Automation Conference (DAC 03).-

### ELECTRICAL TEST IS NOT ENOUGH FOR QUALITY

### BENGT MAGNHAGEN

#### JONKOPINGUNIVERSITY, SWEDEN

#### bengt.magnhagen@ing.hj.se

Electrical test means Functional Test (FT), In Circuit Test (ICT) or Boundary Scan Test (BST) or even a combination of these technologies. However, with modern technology, like SMD (Surface Mounted Devices) technology, BGA (Ball Grid Array) components and extremely small component dimensions, electrical test alone does not meet the quality requierments. Electrical test can not identify bad soldering and bad alignment of components, as examples. Missing decoupling capacitors and so on can not be detected because of it is hard to get physical access for testprobes. Do not forget that digital designs contains a lot of analogue devices!

The tutorial will discuss today test technology with equipment for ICT and BST as well as its pros and cons. And as the addition of this, Inspection. Inspection has traditonally been performed manually but this is not realistic today with board crowded by components. Today Inspection is performed by machine vision. Optical technique named Automated Optical Inspection (AOI) and more advanced X-ray inspection (AXI). AOI and AXI is not the future, it is here today.

EMC/EMI is also a growing challenge and some new ideas will be discussed how to test for these phenomenas.

Підписано до дру\* у 9.09.т004. Формат 60\*84<sup>1</sup>/<sub>«</sub>.

Умов. дру\*. ар\*. ууи4. Облі\*.-вид. ар\*. у0и0. Зам. № т-875. Тираж №0 прим. Віддру\*овано в навчальнофнау\*овому видавничофполіграфічному центрі ХНУРЕ. 6№6иХар\*івипросп. Ленінаи№.