# MINISTRY OF EDUCATION AND SCIENCE OF UKRAINE KHARKOV NATIONAL UNIVERSITY OF RADIOELECTRONICS

ISBN 966-659-088-3

# Proceedings of East-West Design & Test Workshop (EWDTW'04)

Yalta, Alushta, Crimea, Ukraine, September 23 – 26, 2004

© Kharkov National University of Radioelectronics, 2004

## CONTENTS

| EDUARDAS BAREISA, VACIUS JUSAS, KESTUTIS MOTIEJUNAS, RIMANTAS SEINAUSKAS.<br>THE TESTING APPROACH FOR FPGALOGIC CELLS                                            | 8   |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| T. TONNISSON, L. KUUSIK. DATA ACQUISITION MODULE FOR OPTICAL<br>TELECOMMUNICATION TEST INSTRUMENT                                                                | 15  |

| H.J. KADIM. CONDITIONAL ASSERTION OF EVENTS WITH APPLICATIONS TO VERIFICATION OF SOC                                                                             | 17  |

| TOMASZ GARBOLINO, ANDRZEJ HLAWICZKA, ADAM KRISTOF. ANEW IDEA OF<br>TEST-PER-CLOCK INTERCONNECT BIST STRUCTURE                                                    | 23  |

| M. BRIK, J. RAIK, R. UBAR, E. IVASK. GA-BASED TEST GENERATION FOR SEQUENTIAL<br>CIRCUITS                                                                         |     |

| JAAN RAIK, PEETER ELLERVEE, VALENTIN TIHHOMIROV, RAIMUND UBAR. FAST FAULT<br>EMULATION FOR SYNCHRONOUS SEQUENTIAL CIRCUITS                                       | 35  |

| ELENA FOMINA, ALEXANDER SUDNITSON. INFORMATION RELATIONSHIPS FOR<br>DECOMPOSITION OF FINITE STATE MACHINE                                                        | 41  |

| JACEK WYTRÊBOWICZ. AGENTIS VALIDATION – A CASE STUDY                                                                                                             | 48  |

| GENNADIY KRIVULYA, ALEXANDR SHKIL, YEVGENIYA SYREVITCH, OLGAANTIPENKO.<br>VERIFICATION TESTS GENERATION FEATURES FOR MICROPROCESSOR- BASED<br>STRUCTURES         | 57  |

| SHALYTO A.A., NAUMOV L.A. NEW INITIATIVE IN PROGRAMMING.<br>FOUNDATION FOR OPEN PROJECT DOCUMENTATION                                                            | 64  |

| ROMANKEVYCH A., ROMANKEVYCH V., KONONOVA A. SOME CHARACTERISTICS<br>OF FTCS MODELS' BEHAVIOR (IN THE FLOW OF FAULTS)                                             | 69  |

| BOICHENKO Y.P., ZAYCHENKO A.N. IMPLEMENTATION EXPERIENCE OF DSP<br>APPLICATIONS USING FPGA ARCHITECTURE. RESEARCH OF PRACTICAL                                   |     |

| METHODS FOR IMPROVING LOGIC STRUCTURES                                                                                                                           | 70  |

| DROZD A., SITNIKOV V. AN ON-LINE TESTING METHOD FOR A DIGIT BY DIGIT<br>PIPELINE MULTIPLIER WITH TRUNCATED CALCULATIONS                                          | 76  |

| SAPOSHNIKOV V., SAPOSHNIKOV VL., MOROZOV A, OSADTCHI G., GÖSSEL M.<br>DESIGN OF TOTALLY SELF-CHECKING COMBINATIONAL CIRCUITS BY USE<br>OF COMPLEMENTARY CIRCUITS | 83  |

| V. ZAGURSKY, A. RIEKSTINCH. BIST FOR HIGH SPEED ADC                                                                                                              |     |

| V. ZAGURSKY. I.ZARUMBA, A.RIEKSTINCH. A STATISTICAL METHOD FOR<br>ANALOG-DIGITAL SYSTEM TESTING IN TIME AND SPECTRAL DOMAIN                                      |     |

| A. CITAVICIUS, M. KNYVA. MEASUREMENT INSTRUMENTS SOFTWARE<br>REQUIREMENTS                                                                                        | 97  |

| THOMAS KOTTKE, ANDREAS STEININGER A DUAL CORE ARCHITECTURE WITH ERROR<br>CONTAINMENT                                                                             | 102 |

| ORESTA BANDYRSKA, MARTA TALAN, VOLODYMYR RIZNYK. APPLICATIONS OF<br>THE PERFECT COMBINATORIAL SEQUENCES FOR INNOVATIVE DESIGN AND TEST                           | 109 |

| BAZYLEVYCH R.P., PODOLSKYY I.V. INVESTIGATION OF PARTITIONING<br>OPTIMIZATION BY THE OPTIMAL CIRCUIT REDUCTION METHOD                                            | 113 |

| VOLODYMYR G. SKOBELEV. NON-STATIONARY SECRET LOCK: MODEL<br>AND CHECKING                                                                                         | 117 |

| SKOBTSOV Y.A., SKOBTSOV V.Y. EVOLUTIONARY METHODS OF THE TEST<br>PATTERN GENERATION FOR DIGITAL SYSTEMS AT DIFFERENT PRESENTATION                                                    |     |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| LEVELS                                                                                                                                                                               | 123 |

| A. MATROSOVA, S. OSTANIN , A. VORONOV. DESIGNING FPGA-BASED SELF-TESTING<br>CHECKERS FOR ARBITRARY NUMBER OF UNORDERED CODEWORDS                                                     | 130 |

| SHARSHUNOV S.G., BELKIN V.V. FUNCTIONAL TESTING OF MICROPROCESSORS.<br>CASE STUDY                                                                                                    | 135 |

| SAMOILOV V.G., SPERANSKIY D.V., KUPRIYANOVA L.V. DIAGNOSTIC PROBLEM FOR<br>LINEAR AUTOMATA IN INTERVAL STATEMENT                                                                     | 142 |

| EVGENY V.GALICHEV, SERGEY A.KOLOMIETS, VLADIMIR LANTSOV.<br>ARCHITECTURE OF FPGA PROGRAMMING FOR PROTOTYPING TASKS                                                                   | 149 |

| M. SKVORTSOV, M. SERINA, S. MOSIN. AUTOMATED TESTING OF SOFTWARE SYSTEMS                                                                                                             | 150 |

| S.À. KOLOMIETS, I.À. KOLOMIETS, V.N. LANTSOV. DESIGN OF ADPCM-CODEC<br>ON FPGA BASIS                                                                                                 | 152 |

| KONSTANTIN KULIKOV. IP CORES USING FOR CREATION COMPLEX SYSTEM ON A CHIP                                                                                                             | 155 |

| MICHAEL A. TROFIMOV. THE SUBSYSTEM FOR AUTOMATING OF MODEL<br>GENERATION ON VHDL-AMS                                                                                                 | 157 |

| I. A. KOLOMIETS, E. B. KOBLOV, K.V. KULIKOV. RESEARCH OF THE SPEECH SIGNAL PREDICTOR                                                                                                 | 159 |

| N. KASCHEEV, Y. RYABKOV, S. DANILOV. TEST GENERATION FOR SYNCHRONOUS<br>DIGITAL CIRCUITS BASED ON CONTINUOUS APPROACH TO CIRCUIT MODELING                                            | 161 |

| B. SOKOL, I. MROZEK, V. N. YARMOLIK. TRANSPARENT MARCH TESTS TO EFFECTIVE PATTERN SENSITIVE FAULTS DETECTION                                                                         | 166 |

| A.A. USHAKOV, V.S. KHARCHENKO.<br>V.V. TARASENKO. METHODS OF MODELING AND<br>ERROR-TOLERANT DESIGN OF DEPENDABLE EMBEDDED SOPC/FPGA-DECISIONS<br>BY USE OF MULTIVERSION TECHNOLOGIES | 172 |

| A.A. BARKALOV, I.J. ZELENYOVA. RESEARCH OF MULTI-LEVEL STRUCTURE OF THE CONTROL UNIT IN THE BASIS OF PLD                                                                             | 179 |

| E. BUSLOWSKA, V. N. YARMOLIK. TWO-DIMENSIONAL COMPACTION TECHNIQUES<br>FOR RAM BIST                                                                                                  |     |

| ROMAN KVETNY, VLADIMIR LYSOGOR, ALEKSEY BOYKO. INTERVAL MODELLING<br>OF COMPLEX SYSTEMS                                                                                              |     |

| BARKALOV A.A., BUKOWIEC A.F., KOVALYOV S.A. SYNTHESIS OF MEALY FSM WITH<br>MULTIPLE ENCODING OF INTERNAL STATES                                                                      | 193 |

| <b>DOROFEEVA M.U., PETRENKO A.F., VETROVA M.V., YEVTUSHENKO N.V.</b> ADAPTIVE TEST<br>GENERATION FROM A NONDETERMINISTIC FSM                                                         | 197 |

| LADYZHENSKY Y.V., POPOFF Y.V. A PROGRAM SYSTEM FOR DISTRIBUTED<br>EVENT-DRIVEN LOGIC SIMULATION OF VHDL-DESIGNS                                                                      | 203 |

| O. NEMCHENKO, G. KRIVOULYA. USE OF PARALLELISM IN FINITE STATE MACHINES.<br>MATHEMATICAL LEVEL                                                                                       | 210 |

| VOLODYMYR NEMCHENKO. NETWORK SAFETY. PROBLEMS AND PERSPECTIVES                                                                                                                       | 214 |

| KOLPAKOV I.A., RYABTSEV V.G. OPERATIONS OF TRANSFORMATION OF VECTORS<br>INFLUENCES COORDINATES AT DIAGNOSING MODERN DIGITAL SYSTEMS                                                  | 217 |

| RYABTSEV V.G., KUDLAENKO V.M., MOVCHAN Y.V. METHOD OF AN ESTIMATION                                                                            |     |

|------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| DIAGNOSTIC PROPERTIES OF THE TESTS FAMILY MARCH                                                                                                |     |

| MIKHAIL ALEXANDROVICH LODIGIN. THE NEW OPERATIONAL MODE FOR DIGITAL OSCILLOSCOPES                                                              | 225 |

| T.V. GLADKIKH, S. YU. LEONOV. K-VALUE DIFFERENTIAL CALCULUS CAD                                                                                | 227 |

| S.A. ZAYCHENKO,A.N. PARFENTIY, E.A. KAMENUKA, H. KTIAMAN. SET OPERATION<br>SPEED-UP OF FAULT SIMULATION                                        | 231 |

| <b>VOLKER HW. MEYER, AJOY K. PALIT, WALTER ANHEIER.</b> EVALUATION OF SIGNAL<br>INTEGRITY TESTS BASED ON TRANSITION DELAY FAULT TEST PATTERN   | 238 |

| <b>V. A. TVERDOKHLEBOV.</b> THE GENERAL FEATURES OF GEOMETRICAL IMAGES<br>OF FINITE STATE MACHINES                                             | 243 |

| CHUMACHENKO S.V., GOWHER MALIK, KHAWAR PARVEZ. REPRODUCING KERNEL<br>HILBERT SPACE METHODS FOR CAD TOOLS                                       | 247 |

| BONDARENKO M.F., DUDAR Z.V. ABOUT 'SIMILAR-TO-BRAIN' COMPUTERS                                                                                 |     |

| CHIKINA V.A., SHABANOV-KUSHNARENKO S.Y. ABOUT MODIFIED CATEGORIES                                                                              |     |

| M. KAMINSKAYA, O.V. MELNIKOVA, SAMI ULAH KHAN, W. GHRIBI. IMPROVING TEST<br>QUALITY BY APPLYING BOUNDARY SCAN TECHNOLOGY                       | 263 |

| S. HYDUKE, A.A. YEGOROV, O.A. GUZ, I.V. HAHANOVA. CO-DESIGN TECHNOLOGY<br>OF SOC BASED ON ACTIVE-HDL 6.2                                       | 269 |

| KAUSHIK ROY. DESIGN OF NANOMETER SCALE CMOS CIRCUITS                                                                                           | 273 |

| V.I. HAHANOV, V.I. OBRIZAN, A.V. KIYASZHENKO, I.A. POBEZHENKO. NEW FEATURES<br>OF DEDUCTIVE FAULT SIMULATION                                   | 274 |

| LANDRAULT CHRISTIAN. MEMORY TESTING                                                                                                            | 281 |

| SAMVEL SHOUKOURIAN, YERVANT ZORIAN. EMBEDDED-MEMORY TEST AND REPAIR:<br>INFRASTRUCTURE IP FOR SOC DEBUG AND YIELD OPTIMIZATION                 |     |

| <b>A.V. BABICH, I.N. CHUGUROV, YE. GRANKOVA, K.V. KOLESNIKOV</b> . PLANNING OF PASSIVE EXPERIMENT FOR EXPLICIT FAULTS AND BOTTLENECKS LOCATION |     |

| BENGT MAGNHAGEN. ELECTRICAL TEST IS NOT ENOUGH FOR QUALITY                                                                                     |     |

## NETWORK SAFETY. PROBLEMS AND PERSPECTIVES

## VOLODYMYR NEMCHENKO

#### Kharkiv National University of Radio Electronics

#### vpn@narod.ru

Abstract. The necessity of the information protection for networks is shown. Analysis of certain types of the networks attacks is given. Principles of protection of the information in networks and perspectives are shown.

This paper analysis a state of arts in the Network Safety area. The problem is actual especially taking in consideration the escalating of the network attacks amount fixed daily in the Internet. This work estimates the situation with network safety. Summary classification of attacks with the analysis of the basic attacks types is given. Some characteristics of the main types of attacks are shown.

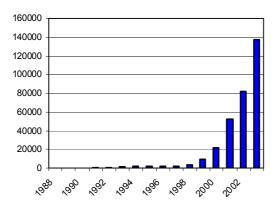

In reality today almost each server is exposed to the attack having place several times in day. The information from CERT (Computer Emergency Response Team) shows the distribution of an amount of the incidents registered in Internet coupled to a network attacks on years since 1988 (6 incidents) till today (137.529 incidents in 2003) [http://www.cert.org]. In total 319.992 cases of network attacks have been fixed during this period. The figure 1 presents this distribution.

Fig. 1. Distribution of an incidents amount on years

The analysis of the literature shows that today there is no the uniform system permitting to

classify possible network attacks. There is a lot of classifications not coupled with each other. In [1] a successful trying to realize systematization of all classifications is made. The brief characteristic of this classification is made in [2].

Before to proceed to the network protocols vulnerabilities reviewing we shall mark that all structures of Internet attacks are shown in this paper very schematically and they cannot be used by malefactors for a realization of real attacks. We use below only public data.

On the other hand, it is necessary to remember ancient wisdom – "who is informed that is armed". In this context the vulnerabilities network protocols knowledge allows users to be ready for any sort of attacks in the web.

Historically the basic network ideas came on 70 - 80th years of past century when it was not given the due attention to the questions of a network safety. The result is that practically all network protocols of OND/IP version 4 are vulnerable for attacks.

We shall examine now the basic types of network attacks.

Ethernet technology using in the LAN (Local Area Networks) uses the common bus topology. It means, that any information circulating on a one segment level can be intercepted and analyzed by any host of this segment. This property can be used by attacking host to pick up a confidential information from an attack victim host. This attack is classified as passive attack [2]. FTP and TELNET protocols are sensible to this attack type because they transmit an information without use of a cryptographic coding.

Another type of attack consists in the substitution of some network subject by another one. In this case when an attacking node sends to the victim a queries on behalf of another subject.

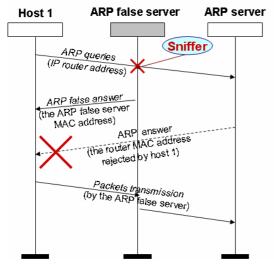

There are two possibilities of the organization of this type attacks. At first, the attacking node realizes the commands on behalf of a control network node, for example, on behalf of the server or of the router. Second, it is the attack realized through the virtual channel established by the TCP protocol. In this case the attacking node substitutes one of the trusted subject of a network. The structure of the ARP false server attack (Address Resolution Protocol) is presented by the figure 2 on the Message Sequence Charts (MSCs) form.

Fig. 2. Structure of the ARP false server attack

The main objective of this attack is to introduce the ARP false server between a host 1 and the real ARP server. As result, the transmitted information can be intercepted or forged by ARP false server.

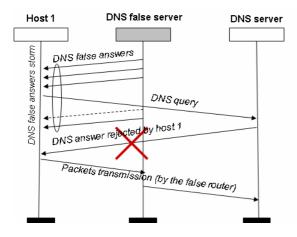

The DNS server (Domain Name System) is used for transformation of a domain name to the IP-address. The basic vulnerability of the DNS server consist in the use of the UDP protocol (User Datagram Protocol) which is not protected against attacks.

There are some possibilities to realize a DNS attack. The figure 3 presents an example of the DNS false server attack structure.

Fig. 3. Structure of the DNS false server attack

The malefactor connects the both nodes through the false router which address was received from the DNS false server. Thus the malefactor intercepts a link. Further all information exchange between hosts will be carried out through the false router, i.e. through the malefactor.

The routing on the network is carried out by such protocols as RIP, OSPF, etc., and the control of a routing is realized by protocols of ICMP family. In a case when a packet cannot be supplied to the destination node because of problems in a web the initial router receives a recommendation to redirect the route. A malefactor can take advantage and replace in the routing table the information concerning a default router. In this case we have the false router attack.

So, we stop our examination of the attack examples end we go on to the question concerning a perspectives of the network safety.

Today the Ethernet technology using a common bus topology is widely applied. Thus all hosts of the same segment have a possibility to gain any information circulating on a common bus. So, the malefactor can use a "sniffer" to intercept a confidential information.

Using a dedicated line segment topology permits to avoid this type of attack. In this case each host of segment should have a proper connection line with each host of the same segment. At the same time, the given structure has no property of flexibility and it is a bounded problem solution.

Other solution is the use of the network switch which connects all hosts of a segment by a dedicated lines. But for all that, in this case the main principle of a network construction survivability is broken. I.e. if switch goes out of operation or is exposed to attack the functioning of all segment will be broken.

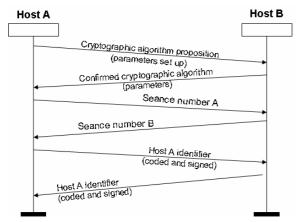

Another perspective to protect information in the web consist in the using of special Internet protocols of new generation. First of all we shall mark that the most protected protocol now is the TCP protocol. The initial TCP connection stage - handshake allows to lower considerably a possibility of attack but does not eliminates it completely [3]. Only use of special encryption methods allows to solve this problem practically. For this purpose it is possible to use the SSL standard (Secure Socket Layer). It is the information encoding algorithm using the open key based on the Diffie - Hellman method [1].

This idea is embodied in the protocol stack of new generation TCP/IPv6. The formation of a cryptographic context is presented in the fig. 4.

Fig. 4. The TCP/IPv6 cryptographic context formation

So, the use of a TCP/IPv6 stack protocols allows to lower a possibility of a network attacks.

Concerning a problem of routing attacks we note that this type of attacks is based on a IP address

falsification of a host sending a packet. For solve this problem each router should test the IP address of the initial host and associate it with an appropriate subnet address. They must correspond each other. But in this case there is a problem of the packet header representation.

We shall mark that network safety contradicts always such web parameters as functionality, accessibility, velocity, etc. Therefore, before to undertake a safety measures it is necessary to determine the necessity level to guard the available information in each concrete case. It may be a price of the undertaken gains above a value of the defended information.

So, the present paper attempts to generalize the available information about the network safety and to show the development paths of this research area.

**References: 1.** *I. Medvedovsky, etc.* Attack against Internet DMK. 1999. **2.** *V. Nemchenko, A. Schaff.* Vulnerabilities and test of Internet protocols / Radioelectronika i Informatika. 2003, No.3, p. 194-195. **3.** Technical details of the attack described by Markoff in NIT. San Diego Supercomputer Center. 1995.

# ELECTRICAL TEST IS NOT ENOUGH FOR QUALITY

## BENGT MAGNHAGEN

#### JONKOPINGUNIVERSITY, SWEDEN

#### bengt.magnhagen@ing.hj.se

Electrical test means Functional Test (FT), In Circuit Test (ICT) or Boundary Scan Test (BST) or even a combination of these technologies. However, with modern technology, like SMD (Surface Mounted Devices) technology, BGA (Ball Grid Array) components and extremely small component dimensions, electrical test alone does not meet the quality requierments. Electrical test can not identify bad soldering and bad alignment of components, as examples. Missing decoupling capacitors and so on can not be detected because of it is hard to get physical access for testprobes. Do not forget that digital designs contains a lot of analogue devices!

The tutorial will discuss today test technology with equipment for ICT and BST as well as its pros and cons. And as the addition of this, Inspection. Inspection has traditonally been performed manually but this is not realistic today with board crowded by components. Today Inspection is performed by machine vision. Optical technique named Automated Optical Inspection (AOI) and more advanced X-ray inspection (AXI). AOI and AXI is not the future, it is here today.

EMC/EMI is also a growing challenge and some new ideas will be discussed how to test for these phenomenas.

Підписано до дру\* у 9.09.т004. Формат 60\*84<sup>1</sup>/<sub>«</sub>.

Умов. дру\*. ар\*. ууи4. Облі\*.-вид. ар\*. у0и0. Зам. № т-875. Тираж №0 прим. Віддру\*овано в навчальнофнау\*овому видавничофполіграфічному центрі ХНУРЕ. 6№6иХар\*івипросп. Ленінаи№.